基于流水線技術的并行高效FIR濾波器設計

摘要:基于流水線技術,利用FPGA進行并行可重復配置高精度的FIR濾波器設計。使用VHDL可以很方便地改變濾波器的系數和階數。在DSP中采用這種FIR濾波器的設計方法可以充分發揮FPGA的優勢。

本文引用地址:http://www.j9360.com/article/191651.htm數字濾波器可以濾除多余的噪聲,擴展信號頻帶,完成信號預調,改變信號的特定頻譜分量,從而得到預期的結果。數字濾波器在DVB、無線通信等數字信號處理中有著廣泛的應用。在數字信號處理中,傳統濾波器通過高速乘法累加器實現,這種方法在下一個采樣周期到來期間,只能進行有限操作,從而限制了帶寬。現實中的信號都是以一定的序列進入處理器的,因此處理器在一個時鐘周期內只能處理有限的位數,不能完全并行處理。基于并行流水線結構的FIR濾波器可以使筆者設計的64階或者128階濾波器與16階濾波器的速度一樣快,其顯著特別是在算法的每一個階段存取數據。FPGA結構使得以采樣速率處理數字信號成為常數乘法器的理想載體,提高了整個系統的性能。由于設計要求的差異,如字長、各級輸出的保留精度等不同,在整個設計過程中,各個環節也有所不同,這就需要根據不同的要求對數據進行不同的處理,如截斷、擴展等,從而設計出既滿足設計需要,又節省FPGA資源的電路。. .

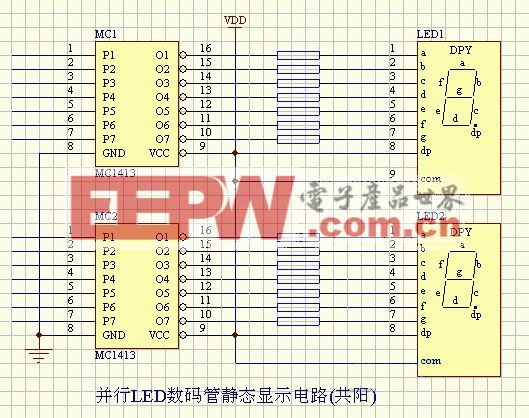

圖1 并行濾波器結構

1 FIR并行濾波器結構

數字濾波器主要通過乘法器、加法器和移位寄存器實現。串行處理方式在階數較大時,處理速度較慢。而現代數字信號處理要求能夠快速、實時處理數據,并行處理數據能夠提高信號處理能力,其結構如圖1所示。

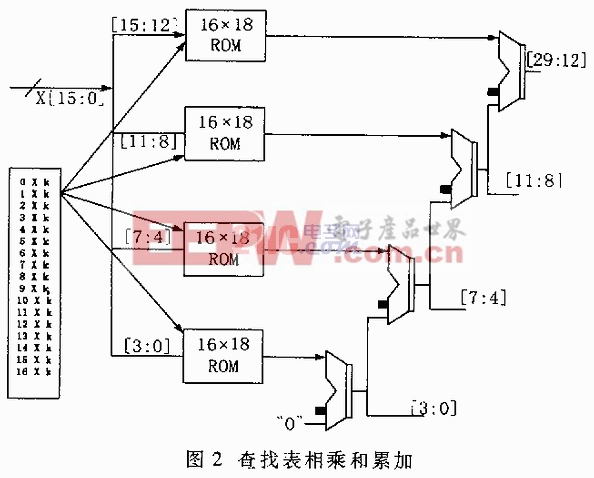

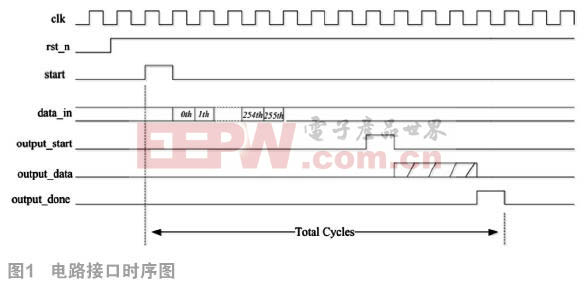

圖2 查找表相乘和累加

從上面的算法可以看出,處理數據的采樣時鐘對每一個抽頭來說都是并行的,并且加法器和移位寄存器采用級聯方式,完成了累加器的功能,綜合了加法器和移位寄存器的優點,而且這種算法的各級結構相同,方便擴展,實現了任意階數的濾波器。算法中,真正點用系統資源的是乘法器。如果將系數量化成二進制,就能采用移位寄存器和加法器實現乘法功能。對于一個特定的濾波器,由于它有固定的系數,乘法功能就是一個長數乘法器。下面將討論乘法器的設計問題。

評論