基于FPGA的移位寄存器流水線結構FFT處理器設計與實

快速傅里葉變換(FFT)在雷達、通信和電子對抗等領域有廣泛應用。近年來現場可編程門陣列(FPGA)的飛速發展,與DSP技術相比,由于其并行信號處理結構,使得FPGA能夠很好地適用于高速信號處理系統。由于Altera等公司研制的FFT IP核,價錢昂貴,不適合大規模應用,在特定領域中,設計適合于自己領域需要的FFT處理器是較為實際的選擇。

本文設計的FFT處理器,基于FPGA技術,由于采用移位寄存器流水線結構,實現了兩路數據的同時輸入,相比傳統的級聯結構,提高了蝶形運算單元的運算效率,減小了輸出延時,降低了芯片資源的使用。在OFDM系統的實際應用中,因它可以采用快速傅里葉變換,能方便快捷地實現調制和解調,故結合MIMO技術,設計的FFT處理器結構,可以很好地應用于2根天線的MIMO-OFDM系統中。

1 FFT處理的應用及DIF FFT算法原理

圖1給出一個2根天線MIMO-OFDM系統中FFT的使用。快速傅里葉變換算法基本上分為兩大類:時域抽取(DIT)和頻域抽取(DIF),這里設計的FFT處理器采用基-2 DIF算法。

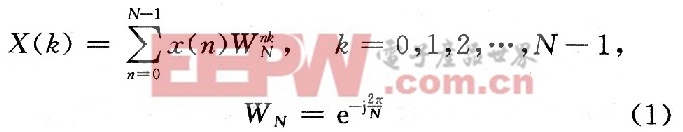

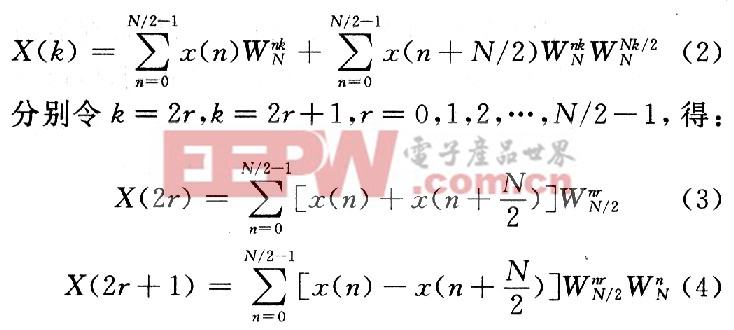

對于N點序列x(N),其傅里葉變換

將x(n)分成上、下兩部分,得:

這樣將兩個N點的DFT分成兩個N/2點的DFT,分的方法是將x(k)按序號k的奇、偶分開。通過這種方式繼續分下去,直到得到兩點的DFT。采用DIF方法設計的FFT,其輸入是正序,輸出是按照奇偶分開的倒序。

2 移位寄存器流水線結構的FFT

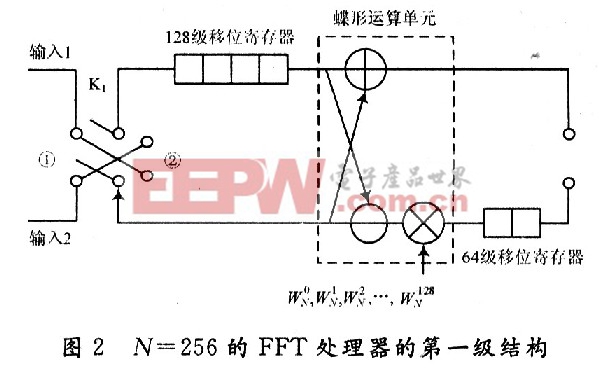

在傳統流水線結構的FFT中,需要將全部數據輸入寄存器后,可開始蝶形運算。在基-2 DIF算法中可以發現,當前N/2個數據進入寄存器后,運算便可以開始,此后進入的第N/2+1個數據與寄存器第一個數據進行蝶形運算,以此類推。

由于采用頻域抽取法,不需要對輸入的數據進行倒序處理,簡化了地址控制,這樣,可以采用移位寄存器的方式,依次將前N/2個數據移入移位寄存器,在N/2+l時刻,第一個數據移出移位寄存器,參與運算。相對于傳統的RAM讀寫方式,采用移位寄存器存儲結構綜合后的最大工作頻率為500 MHz,遠大于RAM方式的166 MHz。

當移位寄存器相繼有數據移出時,在移位寄存器中會出現空白位。此時,引入第二路數據,在第一路數據依次移出進行蝶算時,第二路數據依次補充到移位寄存器的空白位中,為運算做準備。通過這樣一種類似“乒乓操作”的結構,可以使蝶形運算模塊中的數據不間斷地輸入,運算效率達到100%。不同于傳統的“乒乓操作”結構,由于使用移位寄存器,不需要兩塊RAM,可以省掉一半的寄存器。圖2為256點FFT處理器的第一級結構。

評論