基于FPGA的移位寄存器流水線結構FFT處理器設計與實

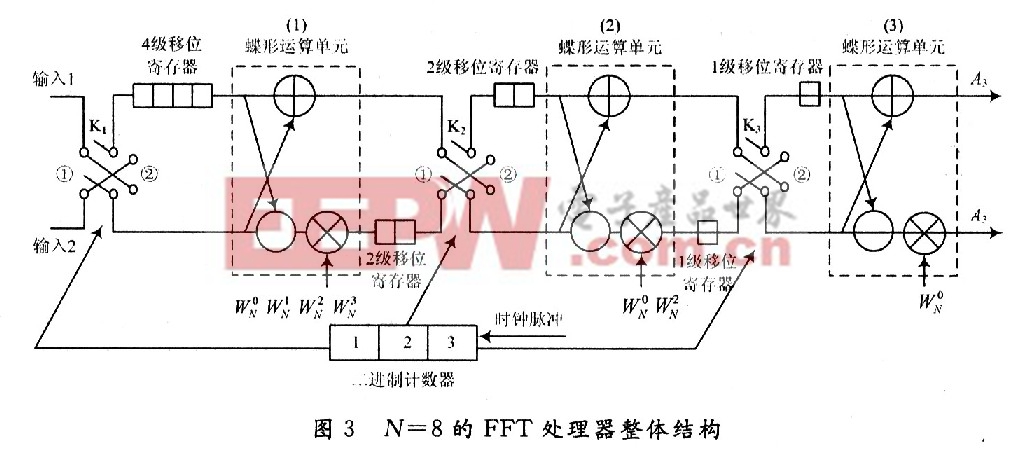

基于上述基本原理,將這種移位寄存器結構擴展到整個FFT系統的各級,可以發現各級使用的移位寄存器數量是遞減的。現使用一個8點結構來進行說明。

如圖3所示,數據由輸入l和輸入2進入第一級。通過開關進行選通控制。由于是N=8的運算,所以各級分別加入4級、2級和1級的移位寄存器。本文引用地址:http://www.j9360.com/article/191644.htm

分兩路來說明運算過程:

將K1打到位置①,第一路數據進入移位寄存器,待第一路的前4個數據存入4級移位寄存器后,第一路進入的第5個數據與移位寄存器移出的第1個數據進行蝶形運算。

由于輸出結果有上下兩路,第二級是一個四點的DFT,所以對于上路的輸出結果x0(0)+x0(4)類似于第一級,直接存入下一級寄存器,為四點運算做準備,下路的輸出,![]() 先存入本級2級移位寄存器中,等到上路的四點運算開始,第二級的移位寄存器有空白位時,移入第二級,為下路的四點運算做準備。所以第一級蝶形運算上路輸出前N/4=2個進入下一級寄存器,下路輸出的數據依次存入本級移位寄存器中。

先存入本級2級移位寄存器中,等到上路的四點運算開始,第二級的移位寄存器有空白位時,移入第二級,為下路的四點運算做準備。所以第一級蝶形運算上路輸出前N/4=2個進入下一級寄存器,下路輸出的數據依次存入本級移位寄存器中。

當第一級的輸出前N/4=2個數據x0(0)+x0(4)和x0(1)+x0(5)存入第二級移位寄存器時,運算便可以開始,這時開關K2打到位置②,此時第一級上路輸出的數據x0(2)+x0(6),即第一級上路輸出的第三個數據與第二級移位寄存器移出的第一個數據,即x0(O)+x0(4)進行蝶形運算,輸出的第四個數據x0(3)+x0(7)與x0(1)+x0(5)進行蝶算。在這個運算過程中,第一級的2級移位寄存器移出數據依次移位存入到第二級的移位寄存器產生的空白位中。

兩個時鐘后,第一級上路輸出的四個數據完成了蝶形運算,K2打到位置①,在接下來的兩個時鐘里,第一級中2級移位寄存器的輸出依次與此時第二級中2級移位寄存器的輸出數據進行蝶形運算,即![]() 與

與![]() ,

,![]() 與

與![]() 完成第一級下路輸出的四個數據的蝶形運算。

完成第一級下路輸出的四個數據的蝶形運算。

此時,第一路在第一級運算后的輸出數據,在第二級完成了全部的蝶形運算。第二級的輸出結果同第一級一樣,蝶形運算的上路輸出前N/8=1個進入下一級寄存器,后一個數據直接進入后一級進行碟算,下路輸出的數據存入本級移位寄存器中。

第三級的運算與第二級和第一級類似,即移入1級寄存器的數據與其后一個數據進行碟算,同時使前一級寄存器的輸出數據進入后一級寄存器的空白位中,然后開關打到位置②,對下路輸出數據進行碟算。

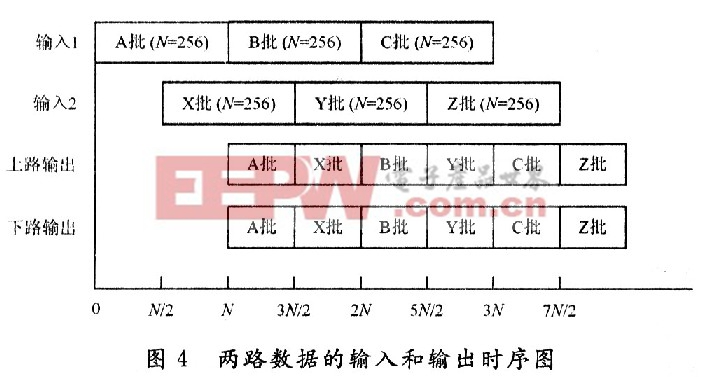

對于第二路數據,通過開關控制,在第二級中,待第一路第一級下路輸出數據進行蝶形運算時,移入寄存器的空白位,為運算做準備,由于前級運算周期是后級運周期的兩倍,對于第二級碟算模塊而言,數據仍然是不間斷輸入的。通過這樣兩路數據的交替運算和存儲,實現“乒乓操作”,從而提高了蝶形運算模塊的運算效率。圖4是256點FFT的具體運算輸入和輸出時序圖。對于只有一路數據的應用場合,可以在前級加入,門控開關和數據緩沖寄存器分成兩路數據,實現一路數據的不間斷讀入。

由于采用移位寄存器結梅,各級寄存器使用的數量都是固定的,即為N/2+N/4。其中,N為該級DFT運算的點數,各級使用的移位寄存器深度逐級遞減,從而大大降低了寄存器的使用數量。

此外,由于各級結構固定,所以大點數FFT只是小點數FFT基礎上級數的增加,而且由于移位寄存器的輸出相對于RAM而言不需要復雜的地址控制,所以這種結構的FFT處理器具有非常好的可擴展性。比如需要實現512點的FFT,只需要在256點的基礎上增加一級即可。

3 具體模塊的設計

3.1 控制與地址產生模塊

由于兩路數據同時輸入,為了防止發生兩路數據間的串擾,對數據的控制顯得極其關鍵。從上面的算法結構分析中知道,由于后級的DFT運算點數是前一級的一半,所以后一級的開關轉換周期也是前一級的一半,基于這種關系,可以使用一個8位計數器的每一位狀態來對各級開關進行控制。最高位控制第一級,同時由于上一級數據進入下一級需要一個時鐘,所以下一級的開關轉換時刻要比上一級延遲一個時鐘周期。

評論