基于EDMA的FPGA與DSP圖像傳輸的設計與實現

摘要 設計了在FPGA與DSP之間進行圖像數據傳輸的硬件結構,介紹了EDMA的工作原理、傳輸參數配置和EDMA的傳輸流程。在開發的實驗平臺上實現了這一傳輸過程。借助TI公司的DSP調試平臺CCS把接收到的圖像數據恢復成圖像,驗證了傳輸過程的正確性和穩定性。

關鍵詞 FPGA;DSP;EDMA;圖像傳輸

數字信號處理器(DSP)是采用數字計算方法對信號進行處理的專用芯片。由于其性能穩定,可大規模集成,編程性高和易實現等優點,被廣泛應用。其中,以圖像處理與DSP技術結合較為普遍,因為圖像所包含的信息數據量大,而DSP的處理速度快,易于實現大量數據高速傳輸的特點能夠滿足這一要求。

目前,圖像處理技術已在通信、信息、電子、航天及軍事等領域得到廣泛應用。與圖像處理有關的系統設計中,FPGA加DSP構架是普遍的使用方法。為充分利用DSP的性能,需要在FPGA中對圖像進行相應的預處理,再把圖像數據傳輸給DSP進行處理。所以FPGA與DSP之間的數據傳輸技術變得不可或缺。

圖像數據傳輸的速度與穩定性對整個系統的性能具有很大的影響。本文介紹了一種基于EDMA的高速穩定的數據傳輸方法,并在TI的DSP開發平臺CCS下,對該方法的性能進行了測試。

1 方案設計

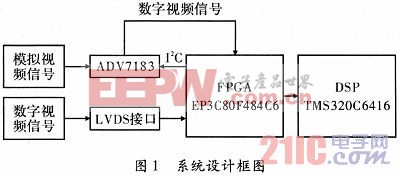

文中圖像傳輸硬件系統結構如圖1所示。該系統中采用Ahera公司的Cyclone3系列FPGA:EP3C80F484C6,Analog Device公司的視頻解碼芯片ADV7183,差分輸入14位數據的LVDS接口和TI公司的TMS320C6416。該系統既可采集模擬視頻信號,又可采集數字視頻信號。模擬信號經過模數轉換芯片ADV7183后變成數字信號,數字信號經由LVDS差分接口進入FPGA。為調試方便,模擬圖像與數字圖像統一使用320×256規格。DSP以EDMA方式接收,經過FPGA預處理后的圖像數據,在CCS平臺下進行顯示以驗證傳輸的正確性。

2 接口電路設計

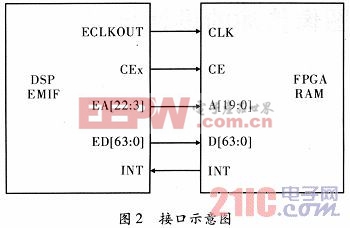

DSP以EDMA方式從FPGA中讀取數據,需要FPGA在內部配置一塊大小適當的存儲空間。FPGA作為一個存儲器,通過DSP的外部存儲器接口(EMIF)與DSP相連。硬件連接如圖2所示。

圖2所示為FPGA與DSP的硬件上連接示意圖。實際使用時,并沒有使用上述所有信號線。FPGA使用到的管腳如下:CLK,CE,A[19:0],D[63:0]和INT。CLK是DSP提供的同步讀寫時鐘,CE是DSP的片選信號,A[19:0]為地址線,D[63:0]地址線。INT為中斷信號。

FPGA與DSP的傳輸機制:FPGA使用QuartusII開發平臺往雙口RAM中寫數,寫滿后用中斷管腳INT來通知DSP讀數。DSP收到FPGA的中斷信號后,開始讀數。讀數期間片選信號CE有效,FPGA把DSP片選信號CE作為雙口RAM的讀使能,在使能期間用DSP提供的時鐘CLK讀取數據。

系統中DSP提供給FPGA的時鐘CLK為100MHz。接收模擬圖像時,圖像數據為8位,只使用D[7:0]8根數據線;接收數字圖像時,圖像數據為14位,使用D[15:0]16根數據線,高兩位置0。數字圖像與模擬圖像均為320×256。

評論