基于EDMA的FPGA與DSP圖像傳輸的設計與實現

3 EDMA傳輸

TMS320C6000系列DSP中的,增強型直接存儲器訪問(EDMA)控制器執行所有二級高速緩存/內存控制器與外設之間的數據傳輸。

EDMA控制器包括事件和中斷處理寄存器、事件編碼器、參數RAM和地址產生硬件電路。事件是觸發EDMA啟動的同步信號,事件寄存器用于捕獲EDMA事件。事件編碼器解決多個事件發生時事件的優先級問題。對應事件的傳輸參數存儲在EDMA參數RAM中,并且傳遞給地址產生硬件單元,進行尋址EMIF或外設執行相應的讀寫操作。

3.1 傳輸流程

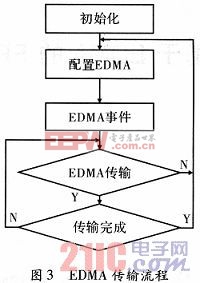

使用EDMA數據傳輸的方法有兩種,一種是CPU初始化的EDMA;第二種是事件觸發的EDMA。所有的EDMA通道都有一個特定的同步事件與之對應,如外圍設備事件、外部硬件中斷或EDMA傳輸完成事件都可以同步觸發EDMA的傳輸。當通道對應的同步事件發生或由CPU同步該通道時,通道就完成一次數據傳輸請求。由事件觸發的EDMA傳輸實時性好,是一種常見的傳輸方式。系統采用的就是事件觸發模式,觸發信號就是FP GA給DSP的中斷信號。圖3為EDMA的傳輸流程。本文引用地址:http://www.j9360.com/article/190722.htm

3.2 EDMA配置

同步事件發生時,EDMA傳輸的數據大小和源目的地址由參數RAM中的參數決定。訪問EDMA的參數RAM時需要通過外圍總線。EDMA傳輸參數,如圖4所示。

選項(OPT)部分主要用于傳輸數據的最小單元、數據傳輸的源地址和目的地址的尋址模式。系統中的最小傳輸單元為1 Byte,源地址設置為一維源,目的地址設置為二維源。數據傳輸模式為幀同步。傳輸數據塊的行數設置255(實際傳輸行數為256),列數設置為320。

源地址(SRC)設置了源數據所在的地址,系統該參數配置為0xA0000000,指向FPGA目的地址(DST)設置了數據要被傳輸到的存儲空間的地址。

實現傳輸過程為把一幅320×256 Byte的圖像從FPGA緩存到了SDRAM中。傳輸14位的數字圖像時,一個像素的圖像數據占用2 Byte,所以要把選項(OPT)中的最小傳輸單元改為2 Byte。

3.3 程序實現

相應的EDMA通道初始化完成后,使能并打開相應的中斷。FPGA每產生一次EDMA同步事件,即往INT管腳發一次中斷信號,EDMA就能完成一次指定要求的傳輸,然后等待下一次同步事件。

評論