基于FPGA實現異步串行通信

摘要:為了適應全數字化自動控制更加廣泛的應用,采用現場可編程門陣列(FPGA)對異步串行通信控制器(UART)進行多模塊的系統設計的方法,使串口通信的集成度更高。對UART系統結構進行了模塊化分解,可分為三個模塊:FPGA波特率發生器控制模塊、FPGA數據發送模塊及數據接收模塊。采用Venlog語言描述硬件功能,利用Xilinx公司的FPGA芯片,在Xilinx ISE Design Suite 13. 4環境下進行設計、編譯、綜合、下載。采用第三方仿真工具ModelSim進行模擬仿真。

關鍵字:FPGA;UART;多模塊;Verilog;Xilinx ISE

異步串行通信(UART)是一種廣泛應用的串行數據傳輸協議,UART的要求是傳輸線少,可靠性高而且傳輸距離遠。UART功能負責從總線采集數據,轉換成傳輸格式,然后發送到串口。也負責從串口接收數據,檢查和刪除附加的位,并傳送結果數據給總線。異步串行通信廣泛的應用于軍事、工業、自動控制、儀器、通信、醫藥、話音圖像處理等眾多領域。現實應用中多采用專用集成芯片實現UART功能,如8250、825 0A、16450、16C451、16C551等。但在實際應用中,一般只需要UART的幾個主要功能,專用芯片成本比較大且造成資源的浪費。近年來隨著電子設計技術的日趨成熟,特別是FPGA在集成度和速度上的大幅提高,可以用一個芯片構成一個復雜的系統。一個芯片就能完成處理計算、通信、控制等多功能,而且成本大幅度降低。根據以上考慮,本文采用FPGA實現UART功能。

1 UART通信原理

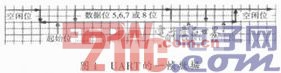

串行通信分為兩種類型:同步通信方式和異步通信方式。UART即通用異步串行通信收發器。UART的一幀數據由起始位、數據位、奇偶校驗位和停止位組成。數據在傳輸過程中是通過一個字符接一個字符進行傳輸來實現通信的。每一幀的信息在傳送前傳輸線處于高電平狀態。在傳送一個字符信息的時候,每一個字符的接收是靠起始位來同步的,字符的前面是一位起始位,首先發送起始位為低電平,一般用下降沿通知收方傳輸開始,然后發送起始位之后的數據位,數據位的傳送先低位后高位,字符本身由5~8位數據位組成。

數據位后面是奇偶校驗位,奇偶校驗位后的是停止位,標志著一幀字符結束。停止位后為高電平,為空閑位,并為下一個字符的開始傳送做準備。在發送、接收數據時,數據的幀與幀之間如果有間隙,就要在停止位之后附加空閑位,停止位后面是不定長度的空閑位。停止位和空閑位都規定高電平,這樣可以保證起始位開始處有一個下降沿。如圖1所示。

1. 1 系統設計與硬件實現

異步通信允許在串行鏈路上進行全雙工的通信。本文把異步通信電路作為一個整體來實現,數據接收經過MAX232進行電平轉換后經FPGA串口模塊的RXD端輸入,由FPGA進行串/并轉換后,8位有效數據進入總線,再進入處理芯片。數據發送經數據處理后經由總線進入FPGA串口模塊,8位有效數據在FPGA中進行并行轉換為串行數據后由TXD端輸出到MAX232的12管腳,在MAX232種經過電平轉換后由TXD端輸出,系統基本結構框圖如圖2所示。

幀格式采用1位開始位,8位數據位,1位停止位,波特率為115 200,根據采用的幀格式,需要發送的數據為10位(1位開始位、8位數據位、1位停止位),在發送完這10位后,就應該停止發送,并使發送端電平處于邏輯1,然后等候下次的發送。

fpga相關文章:fpga是什么

通信相關文章:通信原理

數字濾波器相關文章:數字濾波器原理

評論