基于FPGA和BU-65170的1553B遠程終端設計與實現

摘要:為了滿足載荷與衛星進行可靠通信的目的,設計并實現了基于FPGA和BU-65170協議芯片的1553B遠程終端。自行設計了用于控制BU-65170的主控制狀態機,采用16位零等待緩沖接口模式,使用單消息和雙緩沖模式進行消息傳輸。創新性地引入RS 422總線與1553B總線進行通信,方便測試過程,結果直觀可見。采用專用測試板卡Alta ECD54-1553對系統進行測試,獲得預期的可靠結果。FPGA取代傳統CPU來控制1553B通信并集成數據傳輸功能,采用Verilog HDL硬件描述語言有利于軟件移植,縮短研發周期,提高系統可靠性。

關鍵詞:1553B;FPGA;BU-65170;RS 422

1 1553B概述

MIL-STD-1553B是美國于20世紀70年提出的一種用于戰機的時分控制/命令響應式總線。1553B的網絡拓撲結構如圖1所示,它最多可以掛載32個終端,所有消息共享一條線路,通過采用冗余設計,另一條線路始終處于熱備份狀態,大大提高了可靠性。其字長20 b,數據有效長度16 b,最大信息量長度為32個字,傳輸速度為1 Mb/s,傳輸方式為半雙工方式,采用曼徹斯特Ⅱ型碼。1553B的3種終端類型為:

(1)總線控制器(Bus Controller),總線系統中惟一被安排為執行建立和啟動數據傳輸任務的終端。

(2)遠程終端(Remote Terminal),子系統到總線的接口,在BC的控制下實現命令、數據的接收和發送。

(3)總線監視器(Bus Monitor),能記錄總線上的所有數據,方便備份和查錯,但不參與總線通信。

由于1553B具有可靠性高、實時性好、擴展方便等優點,被廣泛應用于飛機、導彈、衛星、艦艇等航空航天和兵器領域。目前,航天系統大多采用DDC公司的BU-61580/BU-65170協議芯片來實現1553B通信。BU-61580是一款多協議集成接口芯片,由兩個低功耗雙端收發器、協議邏輯、存儲器管理邏輯、處理器接口邏輯及4K×16 B內置共享靜態RAM以及直接面向主處理器的緩存接口組成,能完全實現1553B標準所規定的所有信息傳輸方式。BU-61580和BU-65170的區別在于前者集成了BC/RT/BM功能,后者只能實現RT功能。在此研制的某型號項目作為一個子系統,只要求實現RT功能。因此,選用了BU-65170作為1553B協議芯片。

一般采用CPU來控制BU-65170實現1553B通信,然而CPU只能順序地執行命令,系統硬件不擴展的情況下,難以實現更加復雜的數據處理和控制。隨著航天載荷小型化的要求,數據的運算處理,系統的運行控制及通信,更多地采用FPGA實現,這樣就可以把所有功能集成在一片FPGA芯片中,還能實現代碼的重復利用,提高研發效率。本文采用Xilinx xc6slx75控制BU-65170實現1553B通信,同時因工程項目需要又用FPGA實現了RS422通信,這樣不僅方便測試,使結果直觀可見,還使整個系統事實上成為了1553B總線和RS 422總線適配器。只要稍稍修改代碼,就可以在保留數據處理的功能下將系統移植應用到采用其他通信方式(如RS 232,LVDS等)的子系統上。

2 硬件設計

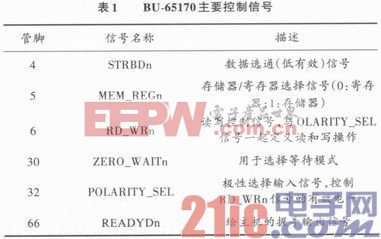

BU-65170共有70個信號管腳,其中主要的控制信號如表1所示。

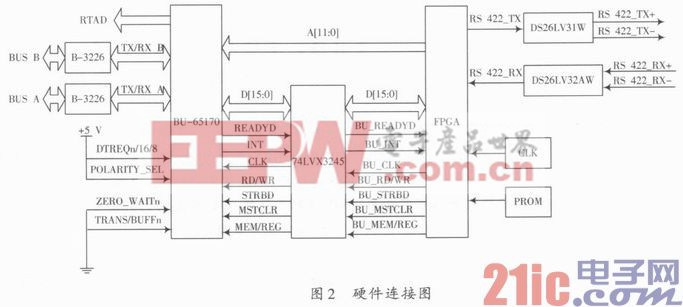

Xilinx的Spartan-6系列xc6s1x75芯片擁有74 637個邏輯單元,11 662個可配置邏輯模塊,280個I/O口以及18 KB的Block RAM模塊,同時擁有豐富的時鐘管理模塊(CMT)、集成存儲器控制模塊等,數據速率高達800 Mb/s。采用XCF32P Flash芯片作為FPGA的PROM,使用MASTER配置模式,這樣在每次上電時程序都會寫入到FPGA中。由于FPGA的I/O口是3.3 V邏輯,而BU-65170是+5 V邏輯,所以需要采用電平轉換芯片74LVX3245進行FPGA和BU-65170之間的邏輯電平轉換。系統的硬件連接如圖2所示。

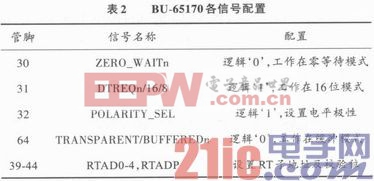

BU-65170有4種接口模式可以選擇,采用16位零等待模式。在此模式下,FPGA接收到BU-65170的READYn信號為低電平后,表示D15-D00上已經呈現讀取的數據,或者D15-D00上的數據已經寫入存儲器或寄存器。BU-65170各信號配置如表2所示。

分別采用DS26LV32AW和DS26LV31W芯片作為RS 422差分接收器和驅動器,UART設計將在邏輯設計中詳細介紹。

3 邏輯設計

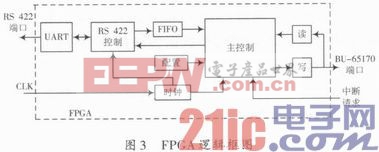

使用Verilog HDL進行編程,在FPGA中實現所需的功能。邏輯總體框圖如圖3所示,下面分別對各個模塊進行詳細介紹。

fpga相關文章:fpga是什么

評論