基于FPGA實現異步串行通信

1.4 FPGA數據接收模塊

數據的接收與數據的發送相比要復雜些。在數據的接收過程中,UART的接收模塊首先要進行的是對起始位的檢驗。一般當接收的第一個是低電平,就標志著一個數據幀的開始,但是在一個數據幀中間也有可能包括一個低電平的位,系統有可能默認為這個低電平為起始位,這樣就會產生一個“假的起始位”。所以,在數據接收的過程當中還要包括對數據起始位的判斷。所以數據的接收過程可以分為空閑狀態、起始位檢測狀態、數據位讀取狀態、讀取停止狀態、準備完成接收和停止位讀取狀態。在判斷起始位低電平后,觸發接收過程,進入數據位讀取狀態使串行總線的輸入數據不斷被讀取并且保存在寄存器內,計數器也到達計數的上限時,接收完成之后并進入準備完成接收狀態,UART控制器會在輸出結果之前對已經接收的數據進行奇偶校驗。然后進入停止位讀取狀態。在每一種狀態,如果使能信號無效時都轉回空閉狀態。最后UART控制器準備下一次的數據接收并重置控制器內的信號檢測器。

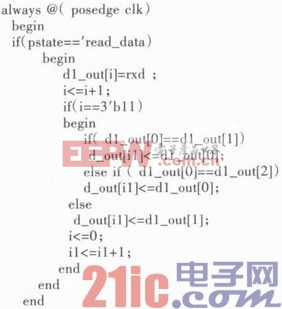

在接收數據過程中,會有一些其他原因使信號產生反轉。為了消除毛刺,在接收數據時,采用3選2的方法消除誤差。也就是這個字符的值是至少有兩次采樣的值相等的值。

采用3選2方法接收數據的程序如下:

接收一幀數據的仿真結果如圖6所示。本文引用地址:http://www.j9360.com/article/189494.htm

在波特率為115 200情況下對UART進行仿真,結果如圖7所示。通過仿真波形可以看出,設計結果正確地發送和接收一幀數據并產生相應的中斷。

2 結論

本文介紹了一種基于FPGA實現異步串行通信功能,采用多模塊的方法實現異步串行通信功能,可以方便用戶根據需要進行裁減、便于理解和調試。本文運用Verilog語言進行設計異步串行并行收發器的IP核電路。

用FPGA實現UART功能,充分利用了FPGA的剩余資源,相對于專用UART芯片,減小系統PCB板的面積,降低系統的功耗,提高系統的穩定性。近年來在電子設計領域中,這種硬件軟件化的方法已經成為一種流行趨勢。該設計采用Xilinx公司的Spartan3E系列中器件XC3S100E。通過ISE軟件進行時序仿真和硬件測試各項通信指標均滿足要求,整個設計的正確性和完整性得到驗證,各項功能均達到預期的要求。

fpga相關文章:fpga是什么

通信相關文章:通信原理

數字濾波器相關文章:數字濾波器原理

評論