基于多軟件平臺協同工作的FIR濾波器設計

摘要:提出了利用多軟件平臺進行FIR數字濾波器的協同設計,改變了傳統的只用硬件電路設計的方法,將整個數字濾波系統的硬件設計趨于軟件化,采用Lattice公司的可編程模擬器件ispPAC20和Altera公司的FPGA設計架構整個FIR濾波器實驗系統。由于ispPAC20和FPGA器件的高度集成化以及結構的可重構、可編程,使開發人員隨時可重復配置滿足各種性能要求的濾波器系統,將整個系統變得更小型化、更易于升級維護且更靈活。

關鍵詞:FIR數字濾波器;FPGA;ispPAC20

0 引言

1992年美國Lattice公司發明了在系統可編程技術,徹底改變了傳統數字電子技術系統的設計和實現方法,開創了數字系統設計的革命性時代。在1999年,Lattice公司又推出了在系統可編程模擬電路,為電子設計自動化技術的應用開拓了更為廣闊的前景。

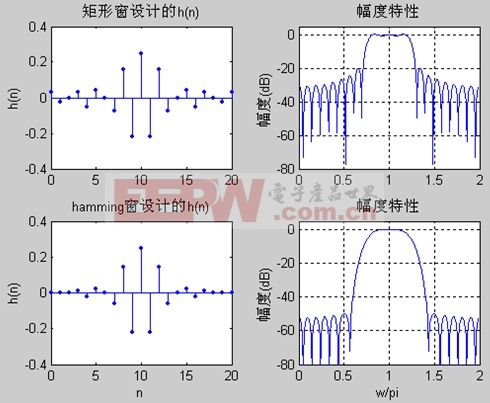

隨著信息科學和計算機技術的迅速發展,數字信號處理在20世紀末期得到了飛躍式的發展。在數字信號處理中數字濾波是重要的環節,經典數字濾波器從實現的網絡結構或者單脈沖響應長度分類,主要分為有限脈沖響應(FIR)和無限脈沖響應(IIR)兩大類;與HR濾波器相比FIR濾波器的計算工作量稍大,但是在保證幅度特性滿足技術要求的同時,很容易做到嚴格的線性相位特性。

1 系統的總體結構設計

由于數字信號處理是用數值運算的方式實現對信號的處理,因此,相對于模擬信號處理,數字信號的處理具有靈活性、高精度和高穩定性、便于大規模集成、而且可以實現模擬系統無法實現的諸多功能。

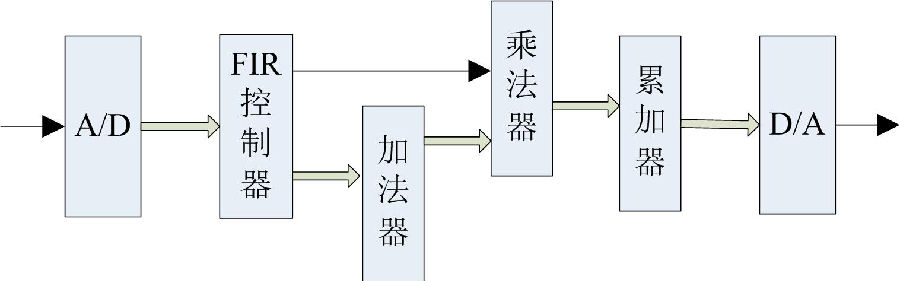

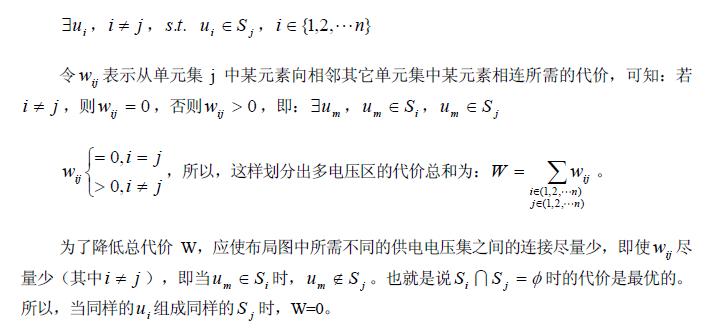

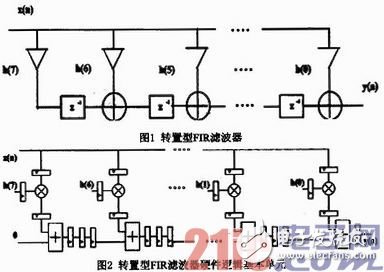

圖1所示為數字濾波器的信號處理過程。數字信號處理的對象諸如語音信號等它們本身也是模擬信號,所以一般先經過緩沖以及模擬信號預濾波,然后利用模-數轉換器(A/D轉換器)將模擬信號轉換成數字信號,再利用FPGA構成的FIR數字濾波器處理轉換后的信號。進一步利用數-模轉換器(D/A轉換器)將數字濾波器處理過的結果轉換為模擬信號供使用。

2 系統各部分功能的設計與實現

2.1 前端緩沖、預濾波以及模數轉換部分結構

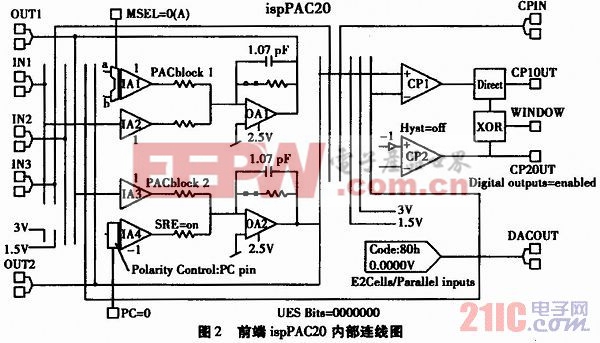

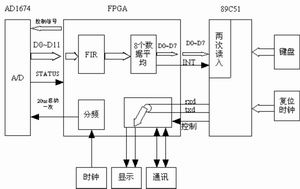

這部分的緩沖以及預濾波由ispPAC20來完成,然后利用FPGA以及ispPAC20中的D/A轉換器、比較器共同構成逐次逼近式A/D轉換器,其中ispPAC20中的電路結構圖如圖2所示。

評論