處理器的高效率電源管理

預測到2010年,處理器將工作在1V和100A電流,到2020年希望處理器的電源電壓將是0.7V和更高電流。處理器工作在1V,100A(或更高)和GHz頻率時的高效電源管理成為設計人員面對的困難任務。

本文引用地址:http://www.j9360.com/article/181455.htm設計人員可以提供低電壓、大電流微處理器電源。但增加高效率(90%或更高)的要求時,采用當今的元件和技術可達到的效率為70%~80%。

VRD配置

VRD(Voltage regulator-down)配置把所有元件直接安裝在計算機母板上,為大部分處理器供電。大部分VRD有8位電壓識別(VID)碼,其8位輸入線直接連接到處理器的相應8個VID引腳。在電壓穩壓器根據感測器的微處理器VID碼,設置處理器所需的工作電壓。處理器也可以采用動態電壓識別來改變時鐘頻率和工作電壓,以響應處理器的工作負載和熱響應。

Intel公司VRD11.0處理器電源供電設計指南中,為5個不同處理器給出所用電源設計指南為:

?最高電源電壓:1.4V~1.425V;

?最大電流:75A~125 A;

?在所有線路、負載和環境條件下,嚴格的輸出電壓調整±5%;

?非常低的紋波,通常小于10mVrmsp-p;

?效率75%~80%;

?快速瞬態響應,與微處理器時鐘頻率一致;

?過壓保護;

?過流(短路)保護;

?過溫保護;

?功耗元件的熱管理;

?相當小的封裝尺寸,使電源可以安置在靠近微處理器負載處。

多相變換器

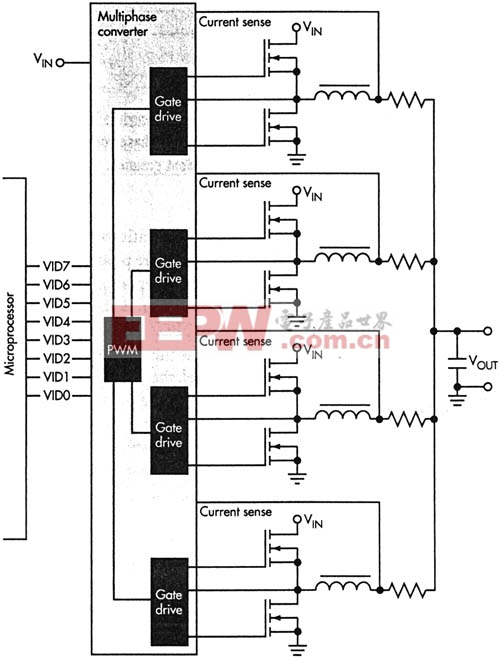

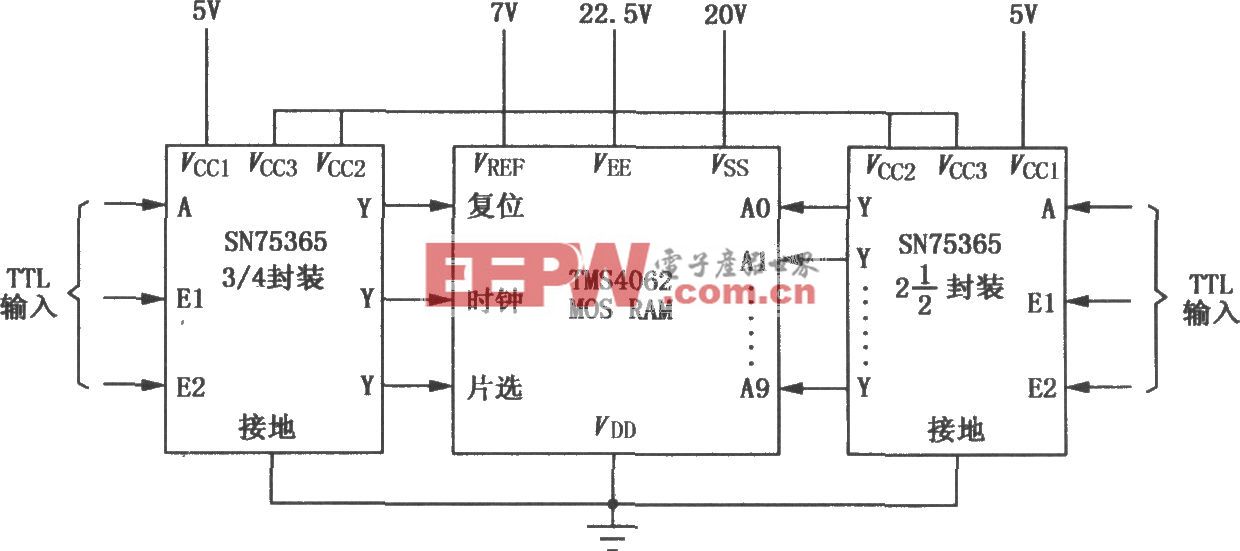

可以滿足當今處理器電源要求的唯一拓撲是多相開關模式變換器。這種變換器采用兩個或更多相同、組合單元,把這些單元輸出連接起來,其輸出是所有單元輸出的總和(圖1)。

圖1 四相電壓穩壓器用分離的柵極驅動器、分立的功率MOSFETs和1個分離的PWM控制器,與微處理器連接靠8位VID碼

為了理解多相變換器的優點,首先看看單相變換器提供大電流和低電壓時的缺點。用一般單相變換器,其輸出汶波和動態響應的改善是靠提高工作頻率。

另外,在較高頻率時,輸出電感器和輸出電容器的物理尺寸和數值變小。在頻率達到一定限值后,變換器開關損耗增大,效率下降。這迫使在工作頻率和效率方面做設計折衷。

為了克服這些單相頻率限制,多相單元工作在一個共同的頻率,但移相結果是變換開關發生在由共同控制芯片控制的規則間隔內。控制芯片交錯排列每個變換器的開關時間,所以,每個變換器開關之間的相位角是360?/n(n是變換器單元數)。因為單元輸出是并聯的,所以,有效的輸出紋波頻率是nxf(f是每個單元的工作頻率)。這種方法具有較好的動態性能和顯著小的去耦電容(與單相系統相比)。

單元的電流均分是必須的。因此,一個單元不能“霸占”大多數電流。理想情況是每個多相單元應該消耗相同量的電流。為了實現相等電流均分,必須監視和控制每個單元的輸出電流。

多相變換器有幾個重要的優點:每個單元提供總輸出功率的1/n,這使得每個相所用的電感器的尺寸數值變小;熱耗分布優點,因為每個單元中的功率半導體只需要處理總功率的1/n,這降低了任何熱點溫度、增加了可靠性,并允許有較高的總功率性能。

另外,等效頻率增高不會招致進一步的開關損耗,這可以采用較小的等效電感,從而縮短負載瞬態周期時間。輸出電容器中降低的紋波電流使輸出紋波電壓變低,這可采用更小或更便宜的輸出電容器。

在選擇相數時,應考慮多相變換器的一些缺點。缺點1,需要較多的開關和輸出電感器,這會導致較高的系統成本;缺點2,需要更復雜的控制,這是因為有多個變換器單元,相互之間不均勻電流均分的可能性是可能的;缺點3,增加了電路布線的復雜性。

隨著工作電流要求的增高,需要有更多的單元相。一個最佳的設計需要折衷考慮相數、每個相的電流、開關頻率、成本、尺寸的效率。更高的輸出電流和更低的電壓,需要更嚴格的輸出電壓調整。多相設計可采用幾種實用的方法。

評論