用于以太網物理層時鐘同步PLL的VCO設計

摘要:研究了一種基于以太網物理層時鐘同步的高帶寬低噪聲壓控振蕩器(VCO),該VCO采用交叉耦合的電流饑餓型環形振蕩器,通過級聯11級環路電路和改善其控制電壓變換電路,優化了VCO的輸出頻率范圍以及降低了輸出時鐘的相位噪聲,完全滿足以太網物理層芯片時鐘電路的性能指標。基于TSMC 3.3 V 0.25 μm CMOS工藝的仿真結果表明,中心頻率為250 MHz時,壓控增益為300 MHz/V,其線性區覆蓋范圍是60~480 MHz,在偏離中心頻率600 kHz處的相位噪聲為-108 dBc。

關鍵詞:VCO;環形振蕩器;電流饑餓型;時鐘同步

0 引言

在以太網中,物理層芯片(Physical Layer Interface Devices,PHY)是將各網元連接到物理介質上的關鍵部件。負責完成互連參考模型(OSI)第I層中的功能,即為鏈路層實體之間進行位傳輸提供物理連接所需的機械、電氣、光電轉換和規程手段。其功能包括建立、維護和拆除物理電路,實現物理層比特(bit)流的透明傳輸等。物理層包括4個功能層和兩個上層接口。兩個上層接口為物理介質無關層接口(MII)和物理介質相關層接口(MDI),在MII的上層是邏輯數據鏈路層(DLL),而MDI的下層則直接與傳輸介質相連。而這些子層的正常工作都離不開一個穩定精確的時鐘同步信號。PLL在物理層芯片的時鐘同步應用中,要求其輸出時鐘帶寬覆蓋范圍廣,電壓控制頻率線性度好,頻譜純度高。在PLL設計過程中,VCO是最為關鍵的設計環節,其性能將直接決定PLL的設計工作質量。近年來,VCO相位噪聲得到越來越深入的研究,各種低噪聲VCO結構不斷涌現,文獻中提到的交叉耦合電流饑餓型VCO便是其中一種。電流饑餓是指電路單元的電流受到電流源的鉗制而不能達到其應有的最大值。本文在其基礎上采用了一種有效控制電壓變換電路,保證原有電路優點的同時擴展了線性度,提高抗噪聲能力,有效降低了相位噪聲。

1 VCO延遲單元工作原理

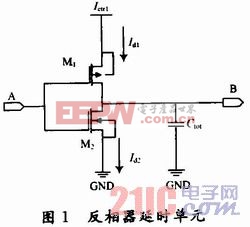

圖1所示為電流饑餓型VCO中的單級結構。PNP管M1和NPN管M2是延遲單元的組成部分,Ictrl是用于控制電容的放電電流Id1和充電電流Id2,他們是構成環形振蕩器的每一級。Ictrl控制著流過M1管和M2管的電流,所以由M1管和M2管構成的延遲單元處于電流饑餓狀態。每一級遲單元處于電流饑餓狀態。每一級的電流都由同一個電流源所鏡像,所以Id1=Id2同時電流大小由輸入控制電流Ictrl控制。

反相延遲主要是2個原因:一個是RC的充電時間;另一個是反相器的預置電壓。而這2個延遲時間的產生都是可以通過調整寬長比來實現。環形反相的次數必須是奇數,這樣電路才不會鎖定導致振蕩失敗。而差動結構的振蕩器級電路數可以是偶數,只要將其中的一級接成不反相的。這種靈活性是差動電路優于單端電路的一個優點。

評論