以太網控制器芯片的設計及實現

網絡控制器芯片的功能與設計實現

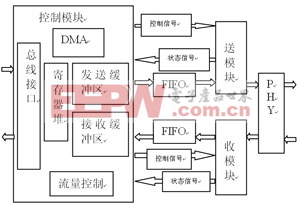

IEEE 802.3協議是針對以太網CSMA/CD標準的傳輸介質物理層(PHY)和介質訪問控制協議(MAC、Media Access Control)來定義的。芯片由PHY、發送模塊、接收模塊、FIFO、控制模塊組成,其中控制模塊包括寄存器堆、DMA(Direct Memory Access)模塊、流量控制模塊、接收緩沖區和發送緩沖區組成。網絡控制器芯片的功能框圖如圖1所示。

1 IEEE 802.3以太網MAC數據幀結構

在發送數據時,發送模塊自動在待傳數據前加上7字節的前導碼和1字節的幀起始定界符,緊隨的是6字節的目的地址和6字節的源地址,然后長度/類型為2字節,接著是數據區,然后是46~1500字節的數據。若發送時,數據長度小于最短長度46字節,發送模塊自動填補,以達到最小長度,最后是4個字節的循環冗余校驗碼。

2 發送模塊

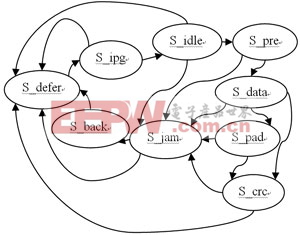

發送模塊的作用就是按照CSMA/CD協議發送數據包。發送模塊狀態機控制協調各個發送子模塊的時序,發送模塊狀態機如圖2所示。

圖2 發送模塊狀態轉換圖

S_defer狀態表示網絡忙,若網絡空閑了,經過最小的幀間隙時間,進入網絡空閑狀態S_idle。若需要發送數據包,經過S_pre,S_data,S_pad,S_crc等狀態發送,在這當中若檢測到沖突信號,就進入S_jam狀態。在S_jam狀態判斷是local collision還是late collision,若是local collision就進入S_back狀態,按照退避算法重發當前數據幀,否則直接進入網絡忙狀態,放棄該幀的發送。

3 接收模塊

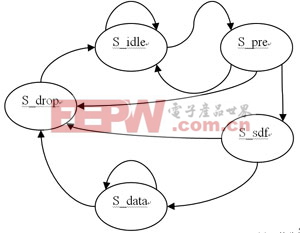

接收模塊的任務就是接收數據幀。物理接口收發器PHY將收到的網絡數據變成二進制數據送給接收模塊,接收模塊再把正確的數據經過接收FIFO和DMA的控制送給接收緩沖區。接收模塊的功能還包括移除接收到幀的前導碼/幀分隔符;比較目的地址,判斷是否丟棄當前數據幀;對接收到的數據包做CRC校驗,判斷傳輸過程中數據是否出錯。接收模塊狀態機是接收模塊的核心,控制協調接收模塊的各個子模塊的工作與時序。接收模塊狀態機如圖3所示。

圖3 接收模塊狀態轉換圖

復位后,狀態機進入S_idle狀態,若數據是無效的,就停留在S_idle狀態,否則進入S_pre狀態。S_pre狀態和S_sdf狀態的作用就是去掉前導碼和幀間隔符。當幀間隔符全部檢測到,進入S_data狀態,在S_data狀態使用字節計數器,記錄所收到數據的字節個數,用于比較目的地址。若目的地址匹配則將接收到的數據寫入到接收FIFO,否則丟棄該幀,不寫入到FIFO。字節計數器的作用還有判斷接收到的數據包是否超過幀的最大長度。若在S_pre狀態、S_sdf狀態或S_data狀態出現數據有效信號無效的情況,都進入到S_drop狀態。

圖4 核心模塊的功能仿真

4 控制模塊

控制模塊包含DMA(direct memory access)模塊、流量控制模塊、緩沖區模塊、寄存器堆模塊和總線接口模塊。DMA模塊的功能是將接收FIFO的數據搬運到接收緩沖區,以及發送緩沖區的數據搬運到發送FIFO。流量控制模塊端口阻塞的情況下丟幀,這種方法是當接收緩沖區開始溢出時,通過將阻塞信號發送回源地址實現的。流量控制可以有效地防止由于網絡中瞬間的大量數據對網絡帶來的沖擊,保證用戶網絡高效而穩定地運行。兩種控制流量的方式:(1)在半雙工方式下,流量控制是通過反向壓力(backpressure),即我們通常說的背壓計數實現的,這種計數是通過向發送源發送jamming信號使得信息源降低發送速度。(2)在全雙工方式下,流量控制一般遵循IEEE 802.3X標準,是由交換機向信息源發送“pause”幀令其暫停發送。緩沖區模塊由一塊32KB的SRAM組成,分為接收緩沖區和發送緩沖區,接收緩沖區和發送緩沖區的大小可以由用戶編程決定。緩沖區以分頁的方式來管理,256B為一頁。主機通過總線接口與芯片交換數據,通過讀寫寄存器堆來控制芯片的工作。

設計驗證

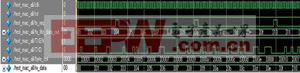

本文給出核心功能的驗證過程。把這些核心功能模塊連接成一個環路(發送模塊直接與接收模塊相連接),發送模塊按照802.3協議發出數據包,接收模塊按照802.3協議處理這些數據包,符合要求的數據包送到(接收緩沖區),這些模塊在Mentor公司的ModelsimSe5.8里面功能仿真波形如圖5所示。

圖5 芯片的實現流程

圖中,clk為系統時鐘;rst為復位信號;tx_req為發送FIFO請求信號,讓DMA從發送緩沖區搬運數據到發送FIFO;tx_fifo_data_out是從發送FIFO里面出來的8數據,發送模塊封裝這些數據,發送給PHY;這里沒有對PHY進行驗證,把發送模塊發出的數據TXD和數據使能TXEN直接與接收模塊數據端和數據有效信號分別相連接;接收模塊把TXD進行串并轉換,得到8為rx_data;byte_cnt為接收到rx_data的個數。

功能仿真通過之后,把核心模塊連接成一個整體(SRAM直接調用Quartus II的IP Core),通過Quartus II綜合以后,下載到FPGA開發板里面。用FPGA模擬網絡控制器芯片,與計算機進行通信。FPGA與PC通過RJ-45相連。應用軟件發一數據包給FPGA,接收模塊接收到數據包后,通過DMA將數據從FIFO搬運到接收緩沖區。一包數據接收完成后,通過附加邏輯,讓FPGA發送出剛剛接收到的數據包,附加邏輯還完成了把接收到的數據按位取反的功能。應用軟件顯示PC收到的數據包,通過比較PC發給FPGA的數據包和FPGA發送給PC的數據包,驗證了核心模塊的功能正確(FPGA的附加邏輯將接收到的數據包進行了按位取反操作)。

芯片實現

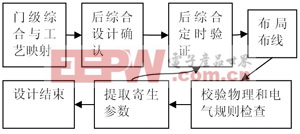

設計驗證通過以后,經過圖5所示的流程,得到整個芯片的版圖。

本次流片采用華虹NEC 0.35μm CMOS工藝,芯片面積為5640μm×5480μm(不計劃片槽和緩沖區),芯片有100個管腳。芯片的右上部分是實現MAC層的數字區,左下區域是華虹NEC提供的IP Core--32KB的SRAM,用作緩沖區,右下區域完成PHY功能,周圍是管腳。

評論