基于DSP的MEMS陀螺儀信號處理平臺設計

0 引 言

本文引用地址:http://www.j9360.com/article/152436.htm陀螺儀是一種能夠精確地確定運動物體方位的儀器,它是現代航空、航海、航天和國防工業中廣泛使用的一種慣性導航儀器,它的發展對一個國家的工業,國防和其他高科技的發展具有十分重要的戰略意義。

近年來隨著MEMS(微機電系統)技術的發展,MEMS陀螺儀的研究與發展受到了廣泛的重視。MEMS陀螺儀具有體積少、重量輕、可靠性好、易于系統集成等優點,應用范圍廣闊。但是目前MEMS陀螺儀的精度還不是很高,要想大范圍應用必須對MEMS陀螺儀的信號進行處理。

本文選用TI公司的TMS320VC33作為MEMS陀螺儀信號處理平臺的核心芯片,同時引入DSP/BIOS實時操作系統提供的多任務處理機制,在對陀螺儀信號進行數據采集的間隙同時對先采集來的信號數據進行處理和傳輸,確保數據采集和處理的實時性,大大提高了信號處理平臺的工作效率,在高速實時數據采集和處理領域具有一定的應用價值。

1.1 信號處理平臺的硬件結構及工作原理

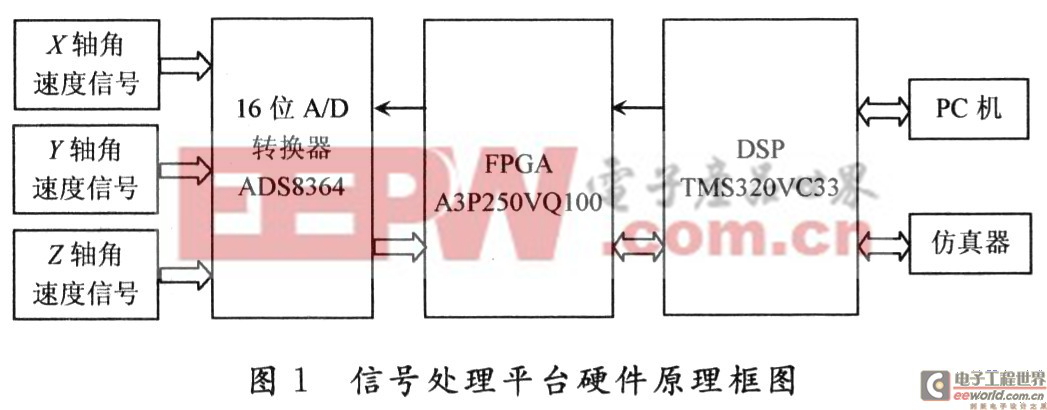

MEMS陀螺儀信號的處理平臺的硬件系統應該包括以下幾個部分:DSP模塊,數據采集模塊,上位機通信模塊和JTAG調試接口模塊。

數據采集模塊由兩部分組成:6路16位模/數轉換器ADS8364和同步時序控制器FPGA(A3P250VQ100)。FPGA(A3P250VQ100)一方面是控制各個單元時序,另一方面是為了對A/D采集來的陀螺信號進行預處理。

模/數轉換器ADS8364通過FPGA與DSPVC33相連,采集三軸陀螺信號。

DSP主要完成對陀螺信號的降噪運算。陀螺信號經DSP處理后再由SCI接口傳送到上位機。

系統設計的原理框圖如圖1所示。

在圖1中三路陀螺模擬信號經過各自的信號調理、抗混迭濾波后進入多通道A/D轉換器,在FPGA的控制下選擇一路信號進行轉換,轉換結果送入FPGA片上FIFO緩存,由DSP讀取數據并進行數字信號處理。同時FPGA對A/D轉換器傳過來的信號進行預處理,再送到DSP進行信號降噪處理,保證了MEMS陀螺信號處理系統處理的實時性。然后DSP把處理后的結果送至上位機和經過串口輸出,完成數字輸出和模擬輸出,滿足不同的應用要求。

1.2 信號處理平臺A/D電路設計

在整個MEME陀螺信號處理平臺中,A/D轉換器是整個系統數據采集部分關鍵核心器件,信號處理系統中選用了美國德州儀器(TI)公司的ADS8364作為MEMS陀螺信號處理平臺的A/D轉換器。ADS8364是TI公司推出的高速、低功耗、6通道16位A/D轉換芯片,共有64個引腳。其時鐘信號由外部提供,最高頻率為5 MHz,對應的采樣頻率是250 kHz。數字電源供電電壓為3~5 V,即可以與3.3 V供電的微控制器接口,也可以與5 V供電的微控制器接口。所以ADS8364非常適合應用在精度要求較高,結構簡單的嵌入式信號處理系統中。

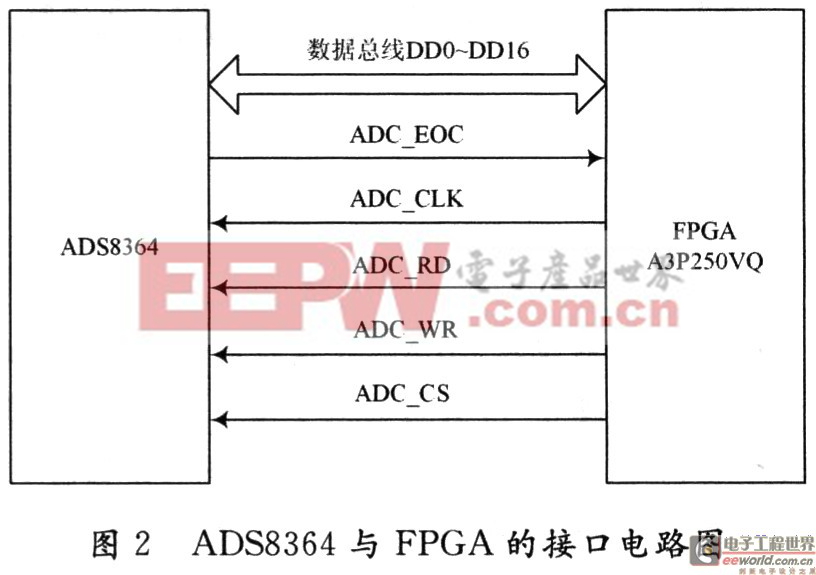

ADS8364的時鐘信號由外部提供,這里由FPGA提供時鐘信號,主要是考慮到FPGA可以靈活地改變時鐘頻率,進而改變系統的采樣頻率。A/D轉換完成后產生轉換結束信號EOC。將ADS8364的BYTE引腳接低電平,使轉換結果以16位的方式輸出。地址/模式信號(A0,A1,A2)決定ADS8364的數據讀取方式,可以選擇的方式包括單通道、周期或FIFO模式。將ADD引腳置為高電平,使得讀出的數據中包含轉換通道信息。考慮到數據采集處理系統的采樣頻率一般較高,如果用DSP直接控制ADS8364的訪問,將占用DSP較多的資源,同時對DSP的實時性要求也較高。因此在本系統設計中,用FPGA實現ADS8364的接口控制電路,并將轉換結果存儲在FPGA中,用DSP實現FPGA芯片的輸出接口。圖2為ADS8364與FPGA的接口電路設計圖。

評論