基于DSP和X5165芯片的非易失性數據存儲設計

數字信號處理器(DSP)的應用日趨廣泛,而重要數據的非易失性保存問題常常是DSP應用中不可缺少的一部分。目前,非易失性的數據保存方法多采用EEPROM(電可擦可編程只讀存儲器)芯片。本文介紹的X5165芯片,可以較好地完成非易失性數據的保存問題。

在某型號交流伺服系統中,要求能夠隨時對各種參數設置進行非易失性保存。考慮到具有串行外設接口(Serial Peripheral Interface,SPI)的芯片使用簡單,占用PCB板面積小等優點,故,采用了XICOR公司生產的16kbit SPI EEPROM芯片來存儲重要數據。

1 TMS320LF2407A的串行外設接口簡介

TMS320LF2407A是TI公司開發生產的16位定點DSP。TMS320LF2407A采用CMOS工藝制造,工作頻率為40MHz,指令周期為25ns。其片內集成了豐富的資源,支持在線編程,非常便于開發設計,且價格低廉,已經進入了傳統單片機所占據的領域。

TMS320LF2407A器件,其片內資源包括了4個引腳的串行外設模塊。SPI是一個高速、同步串行I/O口,它允許長度可編程的位移入或者移出。通常,SPI用于DSP處理器和其它芯片之間的通信。它允許與帶SPI接口的各種類型的芯片相連。SPI的主/從操作也支持多處理器的通信。

TMS320LF2407A的SPI接口有以下特點:

(1)4個外部引腳:SPISOMI(SPI從動輸出/主動輸入引腳),SPISIMO(SPI從動輸入/主動輸出引腳),SPISTE(SPI從動發送使能引腳),SPICLK(SPI串行時鐘引腳)。

(2)發送和接收操作可通過中斷或查詢方法來完成。

(3)可編程波特率,當頻率為40MHz時,波特率可達10Mbps。

(4)數據字長:1~16個數據位。

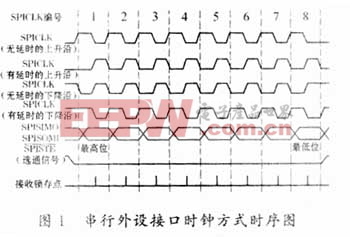

(5)4種時鐘方案(由時鐘極性和時鐘相位控制),如圖1所示。四種不同的時鐘方式如下:

?無延時的下降沿:串行外設接口在SPICLK信號下降沿發送數據,在SPICLK信號上升沿接收數據;

?有延時的下降沿:串行外設接口在SPICLK信號下降沿之前的半個周期時發送數據,在SPICLK信號下降沿接收數據;

?無延時的上升沿:串行外設接口在SPICLK信號上升沿發送數據,在SPICLK信號下降沿接收數據;

?有延時的上升沿:串行外設接口在SPICLK信號上升沿之前的半個周期時發送數據,在SPICLK信號上升沿接收數據。

(6) 同時接收和發送操作。

2 硬件連接電路

X5165的主要特點如下:(1)可編程的看門狗定時器;(2)工作電壓管理,并產生復位信號;(3)SPI接口,波特率可達2Mbps;(4)數據塊鎖定功能和片內偶然性的寫保護功能等。

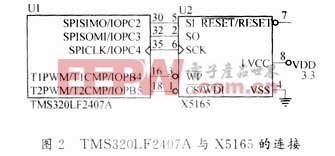

TMS320LF2407A能與多片不同種類的帶SPI接口的芯片相連。本文給出了該芯片與X5165的硬件連接,如圖2所示。通過SPISIMO引腳發送數據,SPISOMI引腳接收數據,SPICLK引腳發送時鐘信號。兩個IO引腳IOPB4、IOPB5用來控制(寫保護)和片選信號。

評論