科研前線 | 刻蝕深淺知否?IBM工藝研發新成果

直擊前線科研動態

盡在芯片揭秘●科研前線

作為應用于下一代集成電路制造工藝的GAAFET器件結構,其多層堆疊的結構增大了刻蝕工藝的復雜性,相關參數的波動難以測量表征。IBM工藝研發團隊通過先進算法與機器學習結合傳統儀器測量發放,實現不通過對整個光學模型解析的計算求解路徑,相關研究成果先行刊載于IEEE Transactions on Semiconductor Manufacturing。

各大晶圓制造廠商已陸續提出基于nanosheet溝道的GAA晶體管器件結構(以下簡稱GAAFET),GAAFET的柵極360°包裹nanosheet溝道四周,相比FinFET更能在器件尺寸縮小的同時改善靜電控制。這樣一個復雜的新結構引入顯著增加了工藝步驟,也對新一代制造設備的改進提出了更多的要求。

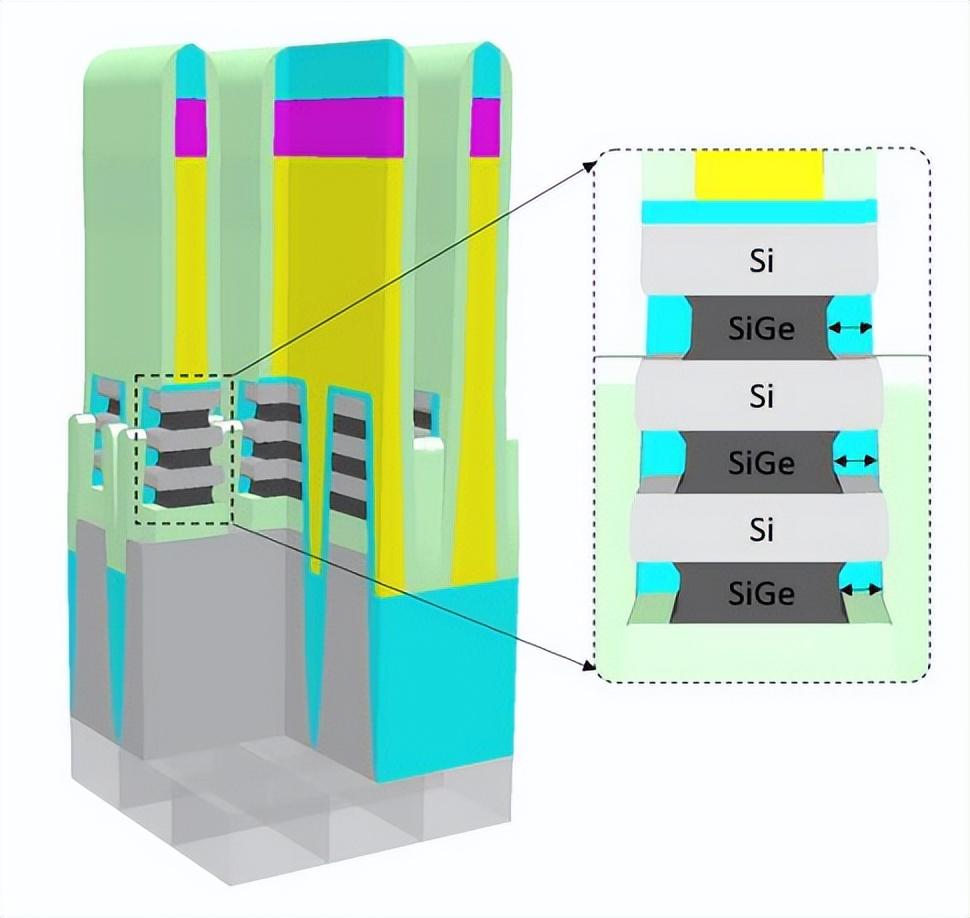

制造nanosheet GAAFET的一個關鍵工藝模塊是內部間隔層的形成,它將溝道與與源/漏區域區分開來,并定義了柵長度。在完成內部間隔層的沉積的前一步關鍵步驟是橫向蝕刻SiGe溝道的犧牲層。這種橫向蝕刻步驟也稱為cavity etch或壓痕(indentation),蝕刻后的完整器件堆棧示意圖如下圖所示。

如果內部間隔層刻蝕過深,柵長和器件性能會受到影響;如果刻蝕太淺,在SiGe去除工藝環節,太薄的內部間隔層可能不足以形成隔離屏障以保護源/漏極區域。除了典型的工藝參數和統計變化外,內間隔層蝕刻過程還取決于SiGe溝道的組分和厚度。然而傳統的基于模型的計量技術很難準確地量化橫向刻蝕量,因為與縮進過程掛鉤的體積變化幅度非常小,難以測量——具體來說一個單元內的體積變化僅為1%左右。

針對這一工藝難題,IBM研發團隊設計了不同的表征方法測量相關參數,其成果以Development of SiGe Indentation Process Control for Gate-All-Around FET Technology Enablement為題發表于IEEE Transactions on Semiconductor Manufacturing,Daniel Schmidt為第一作者及通訊作者。

IBM研究團隊采用多種非破壞性、并行兼容的計量方法以表征SiGe nanosheet溝道側向納米壓痕,具體研究內容包括:

· 制備三種由不同組分的SiGe犧牲層構成的GAAFET器件;

· 采用不同的刻蝕工藝環境以引起壓痕深度的變化;

· 通過干涉光譜法和X射線熒光分析法相結合的散射測量,輔以機器學習算法以量化SiGe納米壓痕測量;

· 給出了平均縮進和sheet溝道縮進兩種方法的解;

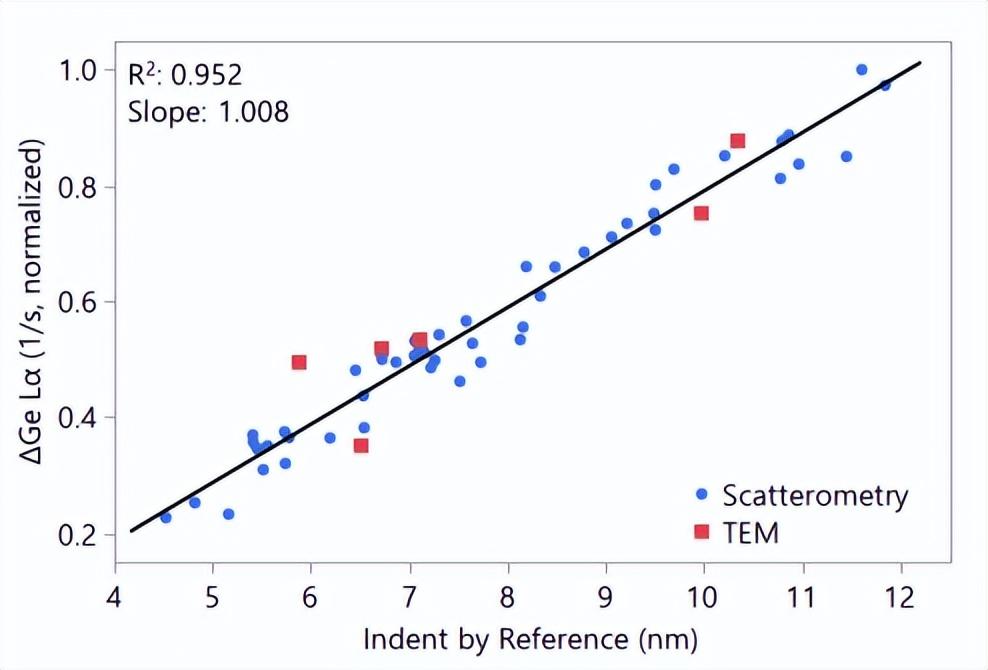

通過機器學習算法通過將熒光分析法測量差值數據與散射光譜相結合,實現了快速求解路徑,從而避免了對全光學模型求解的需要;最終結果顯示,光譜干涉散射法和傳統光學模型結合先進的算法,可以實現與sheet溝道相關數據的良好匹配。

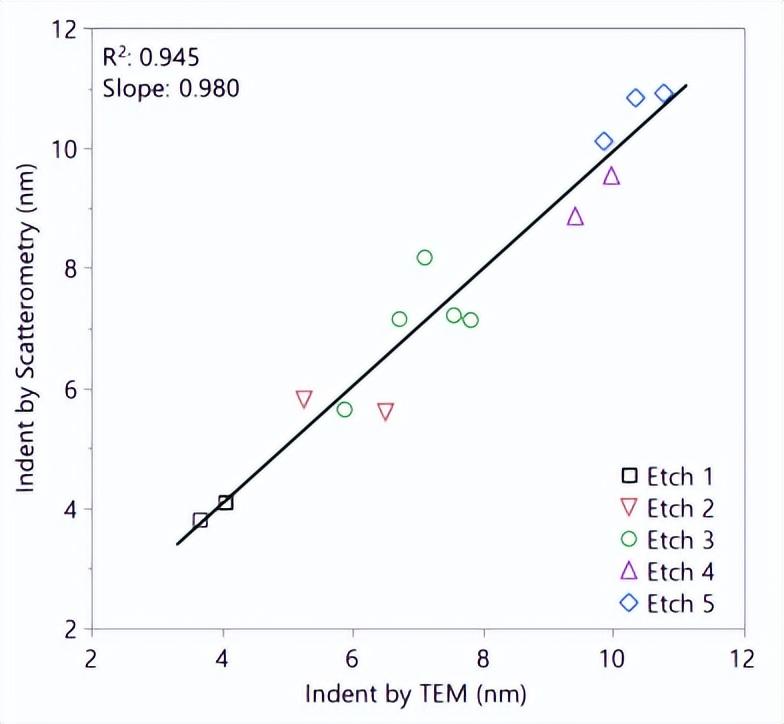

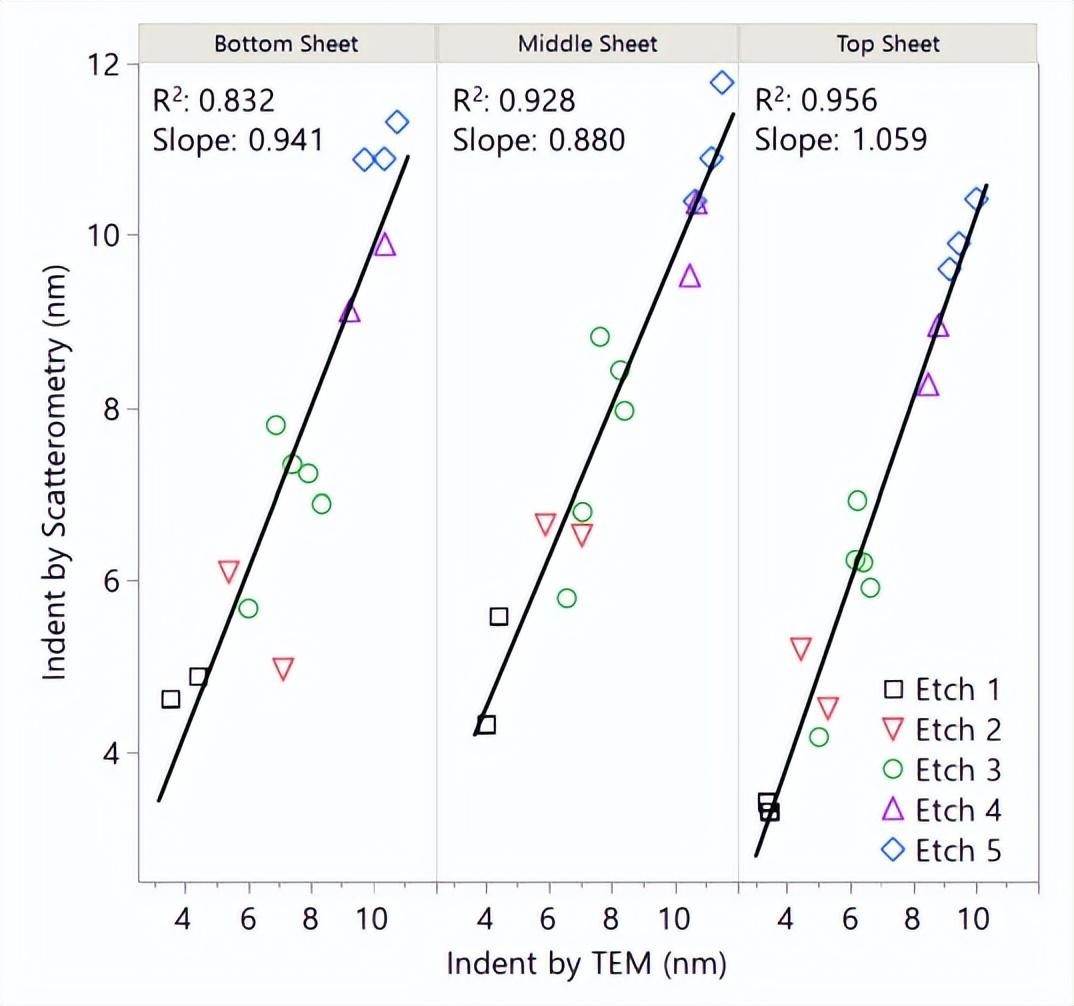

散射法和TEM測定SiGe壓痕的比較

通過歸一化的△Ge Lα作為函數表征 散射法和TEM的基準數據 △Ge Lα:表示刻蝕前后的Ge組分X射線測量結果

基于TEM圖像分析、通過散射法測量獲得的 壓痕分布函數 三個坐標圖分別表示溝道底部、中部和頂部的測量結果

IBM所開發的側向壓痕檢測方法與高通量散射測量相結合,整合了兩種方法的優勢,為工藝開發階段和規模量產階段的工藝流程監測提供了更理想的解決方案:在工藝開發階段,晶圓工藝層堆棧的設計可能隨時變動,這是首選具有高級解釋算法的傳統模型;當工藝原型確定、進入規模量產階段,通過足夠多的橫軸參考數據來訓練機器學習模型更具效益。

*博客內容為網友個人發布,僅代表博主個人觀點,如有侵權請聯系工作人員刪除。