中國上海——2024年1月29日——萊迪思半導體(NASDAQ:LSCC),低功耗可編程器件的領先供應商,今日宣布在由全球600多家供應商和合作伙伴參加的匯川技術年度供應商大會上榮獲“優秀質量獎”。匯川技術表彰的企業提供創新的解決方案,可加速其工業自動化解決方案開發,幫助制造商提高生產效率和加工精度。萊迪思半導體銷售副總裁王誠表示:“在萊迪思,我們專注于與客戶密切合作,通過我們的低功耗、小尺寸解決方案和服務,幫助他們實現設計目標并縮短產品上市時間。我們很榮幸匯川授予我們這一享有盛譽的獎項,我們期待與匯川繼

關鍵字:

萊迪思 匯川 Inovance FPGA 低功耗可編程器件

Verilog 是 Verilog HDL 的簡稱,Verilog HDL 是一種硬件描述語言(HDL:Hardware Description Language),硬件描述語言是電子系統硬件行為描述、結構描述、數據流描述的語言。利用這種語言,數字電路系統的設計可以從頂層到底層(從抽象到具體)逐層描述自己的設計思想,用一系列分層次的模塊來表示極其復雜的數字系統。然后,利用電子設計自動化(EDA)工具,逐層進行仿真驗證,再把其中需要變為實際電路的模塊組合,經過自動綜合工具轉換到門級電路網表。接下去,再用專用

關鍵字:

FPGA verilog HDL EDA

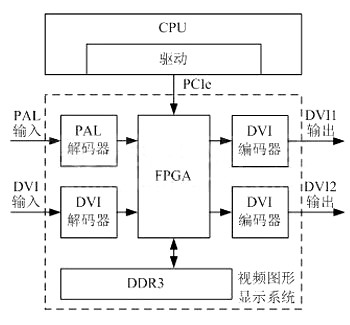

1. 引言Field Programmable GateArray(簡稱,FPGA)于1985年由XILINX創始人之一Ross Freeman發明,第一顆FPGA芯片XC2064為XILINX所發明,FPGA一經發明,后續的發展速度之快,超出大多數人的想象,近些年的FPGA,始終引領先進的工藝。在通信等領域FPGA有著廣泛的應用,通信領域需要高速的通信協議處理方式,另一方面通信協議隨時都在修改,不適合做成專門的芯片,所以能夠靈活改變的功能的FPGA就成了首選。并行和可編程是FPGA最大的優勢。2.核心板

關鍵字:

FPGA Kintex-7 電路設計

...或如何將外圍設備連接到 Spoc。Spoc 內存模型Spoc0 數據存儲器空間深度為 64Kbits。從 0x0000 到 0x0FFF 的地址保留供內部使用。從 0x1000 到 0xFFFF 的地址可供外部外設免費使用。讓我們看看如何使用它!寫入外圍設備寫入事務的寬度可以是 1、8、16 或 32 位。例如:do?#0x1000?->?WA0

do.byte?#0x55?->?@???&nbs

關鍵字:

FPGA Spoc

Spoc 有一個小指令集和一些尋址模式。這使得 Spoc 程序員的模型易于學習。指令集Spoc 目前支持 8 條指令:例子:?inc?RA2??????//?increments?register?RA2?

?dec?A???????//?decrements?accumula

關鍵字:

FPGA Spoc

邏輯使用量小通用架構,可在 Xilinx 和 Altera FPGA 中輕松運行。也可以很容易地移植到ASIC。RISC:小指令集多個累加器,多種數據大小雙寄存器文件每條指令中的條件執行數據存儲器:使用(至少)一個模塊代碼存儲器:使用串行閃存或塊Spoc被設計為幾乎是免費的,即在FPGA中占用很少的空間,并從串行閃存中執行。 許多新的FPGA板卡都已使用串行閃存來配置FPGA。 Spoc 可以使用閃存中未使用的內存空間作為代碼內存。Spoc0Spoc 可以參數化。目前,第一個實現“Spoc0”不是。Spo

關鍵字:

FPGA Spoc

Spoc 是一個 cpu...你猜怎么著?讓我們用它來顯示“Hello world!”。在本例中,您需要一個帶有 RS-232 輸出的 FPGA 板。1. 軟件使用?spoc_asm?編譯以下代碼// First set the stack pointer (required since we use a subroutine below) ?do #0x0C00 -> SPBeginString: ?do #GreetingString -> CSSe

關鍵字:

FPGA Spoc

Spoc CPU軟核:FPGA不僅限于普通的硬件邏輯和狀態機…添加一個軟CPU并創建強大的組合。“ Soft PrOcessor核心”-或“ SPOC”第0部分:世界你好!第1部分:主要特征第2部分:軟件(即程序員)模型第3部分:硬件接口第4部分:軟件示例/技巧?…即將推出第5部分:硬件調試器?…即將推出第6部分:硬件架構?…即將推出

關鍵字:

FPGA Spoc CPU

如何創建多軸CNC銑床FPGA控制器。CNC工程該項目包含7個部分:第1部分:什么是CNC?第2部分:步進控制第3部分:運動控制器第4部分:積分器第5部分:FPGA運動控制器第6部分:運動公式第7部分:運動

關鍵字:

FPGA CNC 步進電機

軸參數每個軸有兩個參數:最大加速度最高速度例如,一個軸的最大加速度為 20mm/s2,最大速度為 50mm/s。 從連續時間的運動公式中,我們可以推導出比,從怠速開始,使用最大加速度,我們將在 2.5 秒后達到最大速度,并在當時達到 62.5mm 的位置。然后使用最大減速度 (-20mm/s2),我們將再移動 62.5 毫米,總共 125 毫米。單軸直線運動假設我們想將一個軸移動一個確定的距離,而不理會其他軸。有兩種情況:短距離或長距離。在第一種情況下(短距離),我們不受最大速度的限制,而在第二種情況下(

關鍵字:

FPGA CNC 運動機芯

由于FPGA運動單元只接受加速度和時間數字,因此PC的工作是計算它們。 由于我們的運動單元具有非常簡單的架構和可預測性,這很容易做到。一點點數學我們可以隨時計算軸的位置和速度,只需知道加速度即可。讓我們為一個軸提供以下四個變量:p?是位置s?是速度a?是加速度t?是時間我們還有增量變量:Δ p 是增量位置(例如,如果位置 p 從 10 移動到 15,則 Δp?為 5)Δs?是增量速度Δa?是 delta 加速度Δt?是增量時間

關鍵字:

FPGA CNC 運動公式

FPGA 設計以下是FPGA運動控制器框圖(顯示三個軸):USB-2 數據在 FIFO 中緩沖,然后進入多路復用器。 由于數據是“打包”的,因此需要解復用器將加速度數據分配到每個積分器的軸。 在積分器之后,脈沖發生器確保階躍/迪爾脈沖具有正確的時序。這是集成商的心聲。generate

for(i=0;?i

關鍵字:

FPGA CNC 運動控制器

秘訣在我們的實現中,PC不會向FPGA發送任何位置或速度信息。 相反,它會發送加速度和時間信息。 FPGA 使用積分器將它們轉換為速度和位置(并相應地驅動階躍/二極管信號)。因此,我們的運動控制器充當加速度積分器。 這很容易實現,因為在FPGA中,積分器只是一個累加器。 以下“C”代碼說明了FPGA在每個時鐘周期的性能:??//?Acceleration?is?known?(provided?by?the?PC)

關鍵字:

FPGA CNC 步進電機 積分器

軟件與硬件運動控制器雖然梯形輪廓易于計算,并且PC通常足以驅動步進信號,但請考慮以下兩個缺點:PC 必須是專用的。PC 引入了機械抖動(由于步進電機的驅動時間不合適,導致軋機晃動或運行速度降低):軟件時序分辨率受并行接口速度的限制。當多個軸一起驅動,步進電機全速運行時,每個軸每秒接收幾個 100000 個脈沖。 由于軟件無法同時在多個軸上實現精確的定時(軟件一次只能做一件事!),因此機械抖動會增加,并且可能需要降低全步進速度才能進行補償。如果您有一臺舊 PC 在壁櫥里無所事事(就像我們大多數人一樣),不介

關鍵字:

FPGA CNC 步進電機 運動控制器

并行接口這是一個典型的業余愛好者 CNC 設置。PC 使用其并行(打印機)接口連接到步進控制器,進而驅動 CNC 銑床的步進電機(有時簡稱為“步進電機”)。假設我們的工廠有三個步進電機,讓我們放大以查看更多細節。PC 為每個步進電機發送兩個信號(步進和方向)。然后步進控制器生成步進輸出(每個步進 4 到 8 根線,具體取決于它們的類型)。PC 必須專用于 CNC 任務,因為步進/Dir 信號的時序必須盡可能精確。 PC 必須在 DOS 模式下運行,或者在 Windows/Linux 模式下運行,但所有其他

關鍵字:

FPGA 步進電機

xilinx fpga介紹

Xilinx FPGA

Xilinx FPGA主要分為兩大類,一種側重低成本應用,容量中等,性能可以滿足一般的邏輯設計要求,如Spartan系列;還有一種側重于高性能應用,容量大,性能能滿足各類高端應用,如Virtex系列,用戶可以根據自己實際應用要求進行選擇。 在性能可以滿足的情況下,優先選擇低成本器件。

Xilinx FPGA可編程邏輯解決方案縮短了電子設備制造商開發產品的時間 [

查看詳細 ]

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473