- 這些功能大部分都集中在Analysis菜單下。 1. Silk to Solder Spacing 這是軟件自動檢驗絲印層與阻焊層間距的功能。Analysis -> Silk to Solder Spacing就會彈出“Check Silkscreen”對話框。 首先

- 關鍵字:

CAM 350 DFM

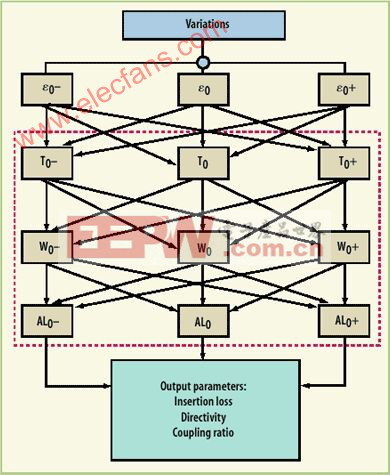

- 低溫共燒陶瓷(LTCC)電路技術支持緊湊型多層設計并被廣泛用于無線應用,特別是在RF模塊和包內系統(SiP)設計中。相對于層壓技術,它具有一系列優勢,盡管其工藝與層壓印刷電路板材料的處理工藝類似。其典型好處是較低的

- 關鍵字:

一次 設計 成功 實現 方法 LTCC DFM 利用

- 中心議題: 可制造性設計(DFM)流程 可制造性設計(DFM)工具 解決方案: 產品PCB制作 產品零部件組裝 產品成品測試

“DFM”-一個由三個字母組成的縮寫,其意義依據你在設計及制造流程鏈中所扮演的角色不同而不同

- 關鍵字:

PCB DFM 可制造性 設計分析

- 時間: 2010年3月17日

地點: 上海東錦江索菲特大酒店

IPC設計師理事會中國分會將于2010年3月17日舉辦2010年度首次PCB設計師活動日。此次活動日將邀請二位理事會的國內專家及一位IPC總部的PCB設計專家做有關PCB設計的專題演講。

三位專家將在設計師活動日做精彩演講,與理事會成員共享交流他們在PCB設計領域的經驗。

誠邀您的光臨!

1. 日程安排

IPC設計師理事會中國分會2010年首次PCB設計師活動日日程安排

- 關鍵字:

PCB DFM CAD

- 現在,重新可編程成為產品設計團隊所必備的能力,他們充分利用這一能力盡快將產品推向市場,盡量延長產品在市時間。FPGA的功能、容量、性能在不斷提高,而功耗和成本顯著下降,足以成為大批量、低成本應用非常可靠的選擇方案之一。

對于采用了單芯片方案且面向全球市場的新產品,應能為不同區域市場提供各種各樣特性的產品。從工業、消費類到軍事

- 關鍵字:

重新可編程 FPGA DFM Altera

- Cadence設計系統公司宣布其多種領先技術已經納入TSMC參考流程9.0版本中。這些可靠的能力幫助設計師使其產品更快地投入量產,提供了自動化的、前端到后端的流程,實現高良品率、省電型設計,面向晶圓廠的40納米生產工藝。

Cadence已經在多代的工藝技術中與TSMC合作,開發參考流程,提供低功耗設計能力和高級DFM方法學。通過參考流程9.0,Cadence將這些性能拓展到該晶圓廠的40納米工藝節點,使用光刻物理分析和強化的統計靜態時序分析能力,此外一直追隨TSMC參考流程的Cadence已經支

- 關鍵字:

Cadence 晶圓 設計 DFM 低功耗

- 全球電子設計創新企業Cadence設計系統公司(NASDAQ: CDNS)今天宣布其多種領先技術已經納入TSMC參考流程9.0版本中。這些可靠的能力幫助設計師使其產品更快地投入量產,提供了自動化的、前端到后端的流程,實現高良品率、省電型設計,面向晶圓廠的40納米生產工藝。

“TSMC和Cadence之間的合作提供了自動化的設計技術,這是在高級工藝節點上實現低風險和快速量產的必要技術,”TSMC設計基礎架構營銷部高級主管S.T. Juang說。

Cadence已經在多

- 關鍵字:

Cadence TSMC DFM

- IC芯片產業在進入納米時代后,生產工藝復雜度和物理極限等局限開始挑戰被稱為定律的“Moor’s Law”。同時,EDA技術的發展不但完全融入到電子產品的設計和定型過程中,并且開始涉足包括存檔、生產、制造、測試等環節,幫助IC產業迎接工藝極限的挑戰。

作為EDA行業的佼佼者,Mentor Graphics公司一年一度的“Mentor Graphics EDA Tech Forum 2007”備受關注。今年的技術論壇以 “洞悉您最復雜的設計挑戰!”為主題在全球18個城市巡回開展。8月31日,Ment

- 關鍵字:

嵌入式系統 單片機 0710_A 雜志_業界風云 DFM MCU和嵌入式微處理器

- 有鑒于半導體產業正試圖解決可制造性設計(DFM)問題,參與月前在美國舉行之SemiconWest展會上的一場小組座談的EDA產業專家表示,可以從可測試性設計(design-for-test,DFT)的技術發展歷程中取經。 該場小組座談會的主持人、市場研究公司GarySmithEDA總裁GarySmith表示:「真正的DFM是個大問號,如果它跟隨DFT的腳步,得花上幾年時間才能在設計社群中扎根。」他指出,半導體公司基本上是把DFT強迫推銷給設計工程師

- 關鍵字:

嵌入式系統 單片機 納米 IC DFM 嵌入式

- CADENCE發布了Cadence Encounter 數字IC設計平臺的最新軟件版本,增加了業內領先的功能特性,包括全芯片優化、面向65納米及以下工藝的超大規模混合信號設計支持,具有對角布線能力的Encounter X Interconnect Option,以及之前已經公布支持的基于Si2通用功率格式(CPF)1.0版本的低功耗設計。新平臺提供了L、XL和GXL三種配置,為先進半導體設計提供更佳的易用性,更短的設計時間以及更高的性能。 “最新版本Enc

- 關鍵字:

CADENCE DFM ENCOUNTER 電源技術 模擬技術 EDA IC設計

- 解決45納米及以下工藝相關變異問題 創新的工藝識別DFM系列產品有助于設計者減少工藝變異的影響, 改善先進半導體的制造設計 全球領先的電子設計自動化(EDA)軟件工具領導廠商Synopsys推出了具備工藝識別功能的可制造性設計(DFM)新系列產品PA-DFM,用于分析45納米及以下工藝定制/模擬設計階段的工藝變異的影響。隨著工藝尺寸的日益減小,先進硅技術將引起更多如應力工程的變異問題,這將越來越影響電路的性能。Synopsys PA-DFM系列的核心產品Seismos 和 P

- 關鍵字:

DFM Synopsys 通訊 網絡 無線

dfm介紹

DFM(Design for Manufacture)是指可制造設計,過去在芯片設計流程中,IC設計業者將電路設計交由晶圓代工廠生產的垂直分工,在進入先進制程技術時遇到了困難,原因是制程技術愈來愈復雜,設計與生產之間的整合溝通必須更加緊密,因此,IC制造業者必須有套完整的DFM,讓IC設計業者得以用其中的設計流程等規范早期便融入設計IC階段中,以提升芯片的設計、生產效率。因此,從制造者的觀點, [

查看詳細 ]

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473