- 摘 要:相位舍位及量化噪聲引起的雜散問題一直是數字頻率合成器研究的重點。針對雜散問題,使用了修正頻率控制字和相位抖動兩種技術,再結合延遲疊加方法,很好地降低了幅度量化雜散和相位舍位雜散,提高了系統的信噪

- 關鍵字:

DDS 頻率合成器

- 機場助航燈恒流調光器系統要求輸出電壓的波形總諧波含量小,穩壓穩頻精度高。本文提出了一種基于DDS技術的SPWM波形產生方法。通過DDS頻率合成的數學模型,介紹了在助航燈恒流調光器系統中基于DDS理論在TMS320LF2407A上實現SPWM波形的原理和方法及利用LF2407A的EVA模塊生成SPWM波形的簡便性,并通過實驗進行了驗證,對機場助航燈新型調光器的設計具有重要的參考意義。

- 關鍵字:

DDS 恒流 調光器 系統

- 信號源是電子產品測量與調試、部隊設備技術保障等領域的基本電子設備。隨著科學技術的發展和測量技術的進步,普通的信號發生器已無法滿足目前日益發展的電子技術領域的生產調試需要。而DDS技術是一種新興的直接數字頻率合成技術,具有頻率分辨率高、頻率切換速度快、切換相位連續、輸出信號相位噪聲低、可編程、全數字化易于集成、體積小、重量輕等優點,因而在雷達及通信等領域具有廣泛的應用前景。

- 關鍵字:

9850 DDS AD 芯片

- 引言

變壓器繞組變形測試儀是保證電力系統安全運行的重要儀器之一,它需要程控的高精度的正弦信號才能正常工作。智能信號源為其提供了頻率按步長值可自動更新輸出的掃頻信號,其性能的特點直接影響著變壓器繞組變形測試儀的研發工作。傳統的方法往往采取壓控振蕩器或分離模塊組成的“直接數字頻率合成器”(DDS),但這些方法大

- 關鍵字:

DDS AD9850 信號發生器 功率放大

- 1 引言 直接數字頻率合成(DDS)是近幾年一種新型的頻率合成法,其具有頻率切換速度快,頻率分辨率高,以及便于 ...

- 關鍵字:

DDS 頻譜分析儀 現場可編程門陣列

- 1 引言

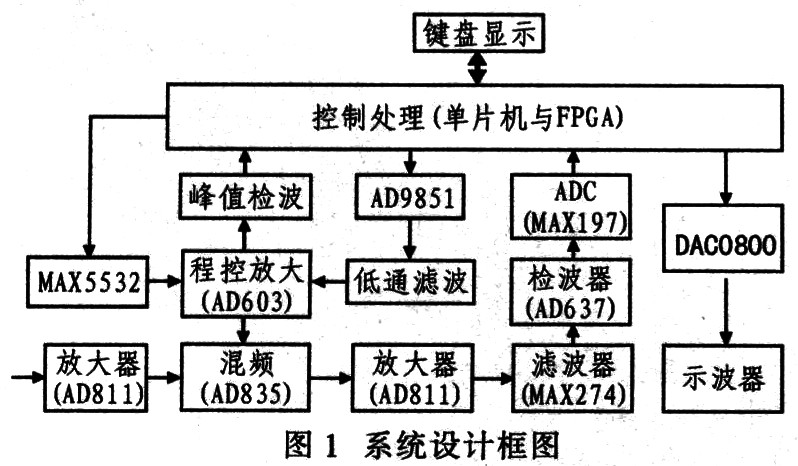

直接數字頻率合成(DDS)是近幾年一種新型的頻率合成法,其具有頻率切換速度快,頻率分辨率高,以及便于集成等優點。在此,設計了基于DDS的頻譜分析儀,該頻譜分析儀依據外差原理,被測信號與本征頻率混頻,實現信號的頻譜分析。

2 系統設計

圖1給出系統設計框圖,主要由本機振蕩電路、混頻電路、放大檢波電路、頻譜輸出顯示電路等組成。通過單片機和現場可編程門陣列(FPGA)共同控制AD985l,以產生正弦掃頻輸出信號,然后經濾波、程控放大得到穩定輸出,與經放大處理的被測信號混頻,再經放

- 關鍵字:

DDS 頻譜分析儀

- 通過對囀音信號進行簡化處理。將復雜的囀音信號轉換為簡單的純音信號。在此基礎上,利用DDS技術對純音信號進行數字化處理,并通過CVI強大的信號分析和處理函數得到單周期純音信號所對應的離散幅值。同時設計了硬件電路。對構造的囀音信號進行輸出。此外,還提出了對該系統進行拓展的可行性及優化的著眼點。

- 關鍵字:

信號發生器 8051F330 DDS 基于 數字處理 8051F330 放大器 單片機

- 為了滿足目前對數據處理速度的需求,設計了一種基于FPGA+DDS的控制系統。闡述了系統硬件實現方法,給出了相關的軟件設計例程。并對DDS AD9911各個控制寄存器的設置與時序進行詳細說明,最后給出了實驗結果。

- 關鍵字:

FPGA DDS 控制設計

- 提出了一種基于DDS(Direct Digital Synthesize)AD9850的頻率、相位、幅值均可調節的正弦信號發生器。該正弦信號發生器采用AT89S52單片機為控制器,D/A轉換器TLC5615與乘法器AD534相結合。實現輸出正弦信號幅值可控,采用AD8ll控制輸出正弦信號電壓幅值,產生50 H2~3 kHz頻段的正弦波,步進頻率為50 Hz。該信號發生器可應用在交變磁場測量儀和試驗儀器、工程設計的函數發生器中。

- 關鍵字:

DDS 可調 信號發生器 設計 基于 模擬 AD9850 TLC5615

- 多年以來,作為業界主流產品的模擬PLL已被熟知,模擬PLL性能穩定,可為頻率合成和抖動消除提供低成本的解決方案,工作頻率高達8GHz及以上。然而新興的基于直接數字頻率合成(DDS)的數字PLL在某些應用中極具競爭力。本文比較了模擬PLL和基于DDS的數字PLL之間的差異,以及如何利用這些差異來指導設計人員選擇最佳的解決方案。

數字PLL利用數字邏輯實現傳統的PLL模塊。雖然實現數字PLL的方法有很多,但本文只介紹基于DDS的數字PLL架構。

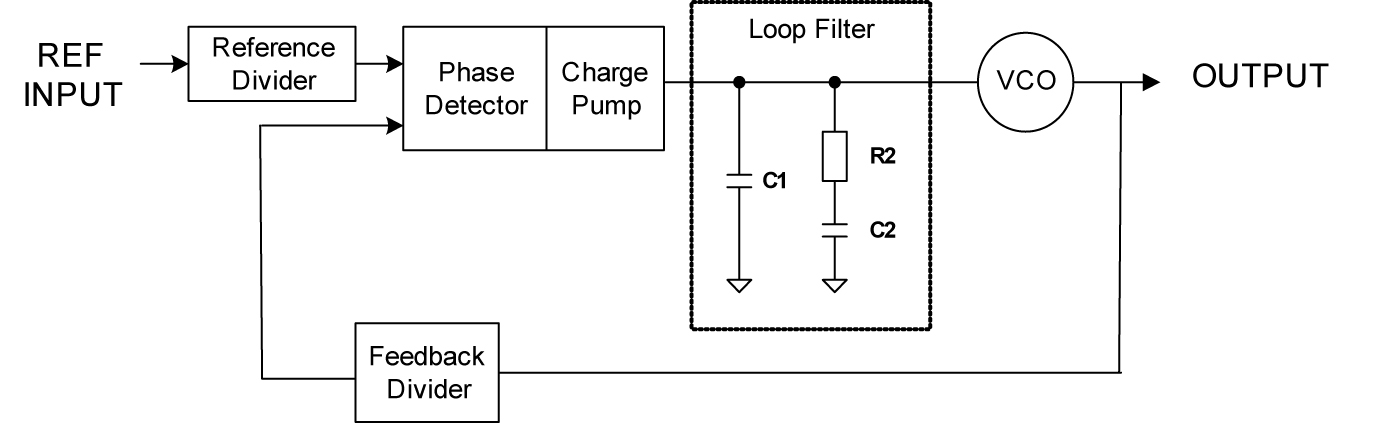

圖1 典型的模擬PLL結構框圖

- 關鍵字:

PLL DDS 分頻器 鑒相器 DAC VCO

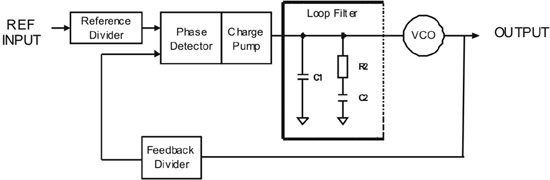

- 多年以來,作為業界主流產品的模擬PLL已被熟知,模擬PLL性能穩定,可為頻率合成和抖動消除提供低成本的解決方案,工作頻率高達8GHz及以上。然而新興的基于直接數字頻率合成(DDS)的數字PLL在某些應用中極具競爭力。

數字PLL利用數字邏輯實現傳統的PLL模塊。雖然實現數字PLL的方法有很多,但本文只介紹基于DDS的數字PLL架構。

圖1 典型的模擬PLL結構框圖

圖1所示的是典型的模擬PLL。輸入信號首先進入參考分頻器,參考分頻器可降低輸入鑒相器的信號頻率。在PLL中,參考分頻器的

- 關鍵字:

DDS 數字PLL

- 引言

在數字信息傳輸中,基帶數字信號通常要經過調制器調制,將頻率搬移到適合信息傳輸的頻段上。2FSK就是用數字信號去調制載波的頻率(移頻鍵控),由于它具有方法簡單、易于實現、抗噪聲和抗衰落性能較強等優點,因此在現代數字通信系統的低、中速數據傳輸中得到了廣泛應用。

直接數字頻率合成技術(DDS)將先進的數字處理技術與方法引入信號合成領域。DDS器件采用高速數字電路和高速D/A轉換技術,具備頻率轉換時間短、頻率分辨率高、頻率穩定度高、輸出信號頻率和相位可快速程控切換等優點,可以

- 關鍵字:

數字信號 調制器 DDS 單片機控

dds介紹

DDS的簡單介紹

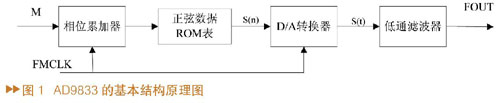

DDS同 DSP(數字信號處理)一樣,是一項關鍵的數字化技術。DDS是直接數字式頻率合成器(Direct Digital Synthesizer)的英文縮寫。與傳統的頻率合成器相比,DDS具有低成本、低功耗、高分辨率和快速轉換時間等優點,廣泛使用在電信與電子儀器領域,是實現設備全數字化的一個關鍵技術。

一塊DDS芯片中主要包括頻率控制寄存器、高速相位累加器和正弦計算 [

查看詳細 ]

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473