基于ARM和FPGA的聲納波形產生系統設

1、引言

本文引用地址:http://www.j9360.com/article/152568.htm最佳聲納系統的設計需要從聲納波形、聲納信道和聲納接收機三方面進行綜合考慮[1]。在聲納信道一定的假設下,需要設計最佳聲納波形和最佳接收機,使聲納系統能在給定的聲納環境中對目標有最佳的檢測效果。工作在淺水中的主動聲納,其性能主要受限于混響級。根據波形選擇與信道匹配的原則,針對混響信道,所選的聲納波形應使其模糊度函數盡量與混響信道散射函數不重合,而與聲傳輸信號散射函數盡量重合[2]。基于這樣的原則,常用的聲納信號單頻信號(CW)、線性調頻信號(LFM)抑制混響的能力比較如下:在檢測靜止或低速目標時,LFM和短CW較長CW有更好的混響抑制能力,但短CW波只適合近距離目標;在檢測高速運動目標時,長CW脈沖是最合適的信號形式[2]。由此可見,主動聲納要完成目標捕獲、識別、跟蹤等不同任務,需要發射不同的聲納波形。同時針對遠距離、低速和高速運動等目標的不同情況,也需要靈活的選擇聲納波形。正是基于這樣一種需求,本文把具有強大控制能力的微處理器ARM與具有靈活波形產生能力的直接數字頻率合成技術(DDS)結合起來,用FPGA實現DDS技術,設計出了基于ARM和FPGA的聲納波形產生系統。

2、DDS基本原理

隨著微電子技術的迅速發展,具有頻率切換時間短、頻率分辨率高、相位變化連續、易實現信號的多種調制等諸多優點的DDS技術,有了廣闊的應用前景。DDS技術可以理解為數字信號處理中信號綜合的硬件實現問題,即給定信號幅度、頻率、相位等參數,產生所需要的信號波形。

DDS的基本結構包括:相位累加器、相位-幅值轉換電路、數模轉換電路及低通濾波器等。相位-幅值轉換電路根據轉換方式的不同可分為兩大類[4]:(1)ROM查找表法。ROM中存儲有不同相位對應的幅度值,可根據相位累加器輸出的相位值尋址ROM,輸出對應的幅值序列。 (2)計算法。對相位累加器輸出的相位值,通過數學計算的方法得到對應的幅值。常用的實時計算方法有泰勒級數求值法、反函數求值法、CORDIC算法等。

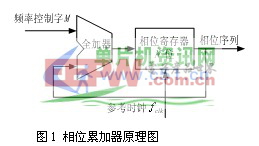

相位累加器是DDS電路中核心的模塊,在工程實踐上一般用數字全加器和數字寄存器的組合來實現,是一個典型的反饋電路。如圖1所示。

其中, 為頻率控制字, 為相位累加器的位數,fclk為系統參考時鐘。相位累加器的工作過程為:每來一個參考時鐘脈沖,頻率控制字 與相位寄存器輸出的相位數據累加一次,累加后的相位一方面反饋到全加器的輸入端,以使全加器在下一時鐘的作用下繼續與頻率控制字 相加;另一方面作為采樣地址值送入ROM查找表。如此循環,當相位累加器累加滿量后,就會產生一次溢出,ROM存儲器的地址正好循環一次,完成一個周期性的動作,這個周期就是DDS合成信號的周期,累加器的溢出頻率就是合成信號的頻率[8]。圖2為相位累加過程示意圖及對應輸出的占空比1:1的CW波。

評論