dds介紹

DDS的簡單介紹

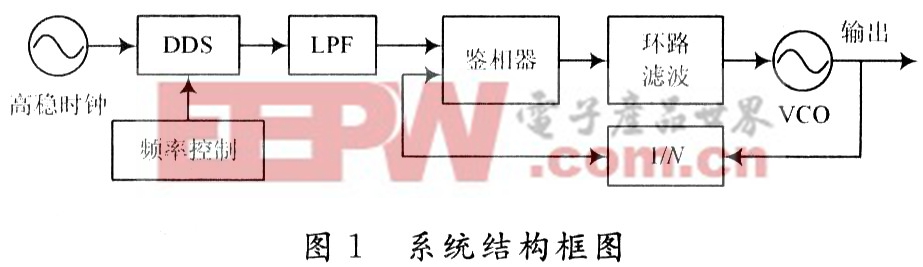

DDS同 DSP(數字信號處理)一樣,是一項關鍵的數字化技術。DDS是直接數字式頻率合成器(Direct Digital Synthesizer)的英文縮寫。與傳統的頻率合成器相比,DDS具有低成本、低功耗、高分辨率和快速轉換時間等優點,廣泛使用在電信與電子儀器領域,是實現設備全數字化的一個關鍵技術。

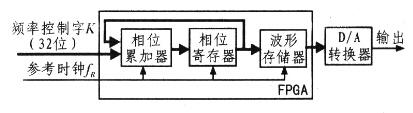

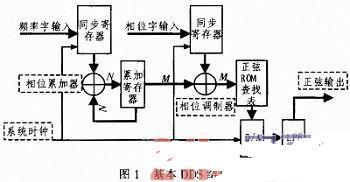

一塊DDS芯片中主要包括頻率控制寄存器、高速相位累加器和正弦計算 [ 查看詳細 ]