基于DDS的數字PLL

多年以來,作為業界主流產品的模擬PLL已被熟知,模擬PLL性能穩定,可為頻率合成和抖動消除提供低成本的解決方案,工作頻率高達8GHz及以上。然而新興的基于直接數字頻率合成(DDS)的數字PLL在某些應用中極具競爭力。本文比較了模擬PLL和基于DDS的數字PLL之間的差異,以及如何利用這些差異來指導設計人員選擇最佳的解決方案。

本文引用地址:http://www.j9360.com/article/89813.htm數字PLL利用數字邏輯實現傳統的PLL模塊。雖然實現數字PLL的方法有很多,但本文只介紹基于DDS的數字PLL架構。

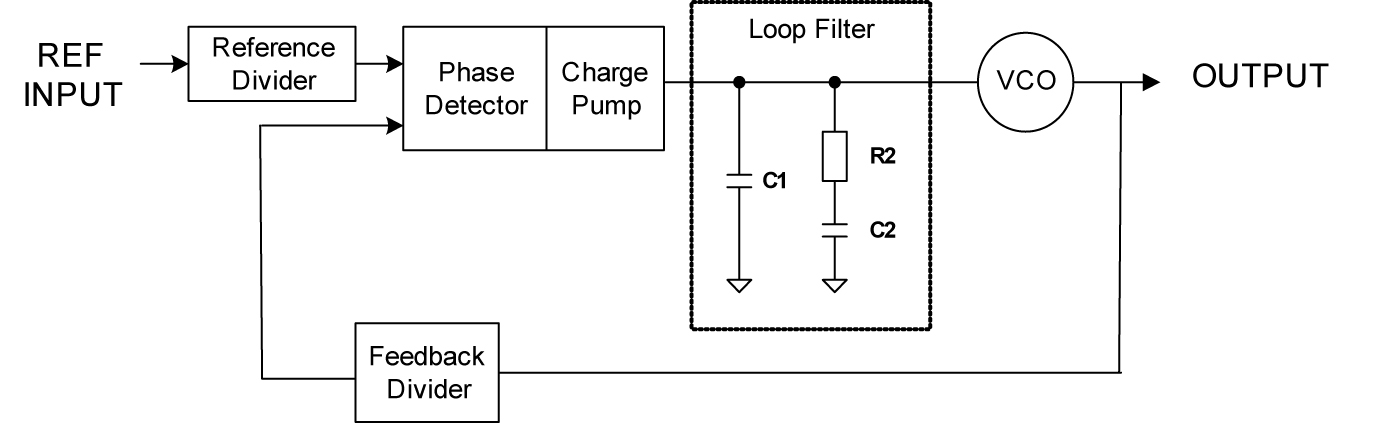

圖1 典型的模擬PLL結構框圖

圖中:REF INPUT-參考輸入;Reference Divider-參考分頻器;Phase Detector-鑒相器;Charge Pump-電荷泵;Loop Filter-環路濾波器;OUTPUT-輸出;Feedback Divider-反饋分頻器

圖1所示的是典型的模擬PLL。輸入信號首先進入參考分頻器,參考分頻器可降低輸入鑒相器的信號頻率。在PLL中,參考分頻器的設置非常關鍵。如果設計人員必須使用大的分頻比降低鑒相頻率來生成期望的輸出信號,那么環路帶寬就會受到限制。下文將會對這一點進行詳細說明。

在模擬PLL中,鑒相器產生上升或下降的電流脈沖,其持續時間與參考信號和反饋信號的相差成正比。而對于數字PLL,鑒相器的輸出是與輸入參考信號沿和反饋信號沿的時間差成正比的數字量。這些數字量被送入數字環路濾波器,完成濾波并對鑒相器的輸出進行積分。環路濾波器的參數是數字型的,但可以較容易的改變,同時,與模擬PLL不同,其大小沒有限制。另外,數字鑒相器不受熱噪聲、老化或漂移以及電荷泵失配或泄露的影響。而在模擬PLL中,當電荷泵中的晶體管沒有完全關斷或其它泄漏導致壓控振蕩器(VCO)中有不希望的電壓變化時,都會發生電荷泵泄漏。另外,模擬PLL中電荷泵泄漏和驅動器上升/下降電流的失配會導致輸出信號的頻譜在鑒相器頻率上出現雜散,而數字PLL由于沒有電荷泵,因此避免了這種現象發生。

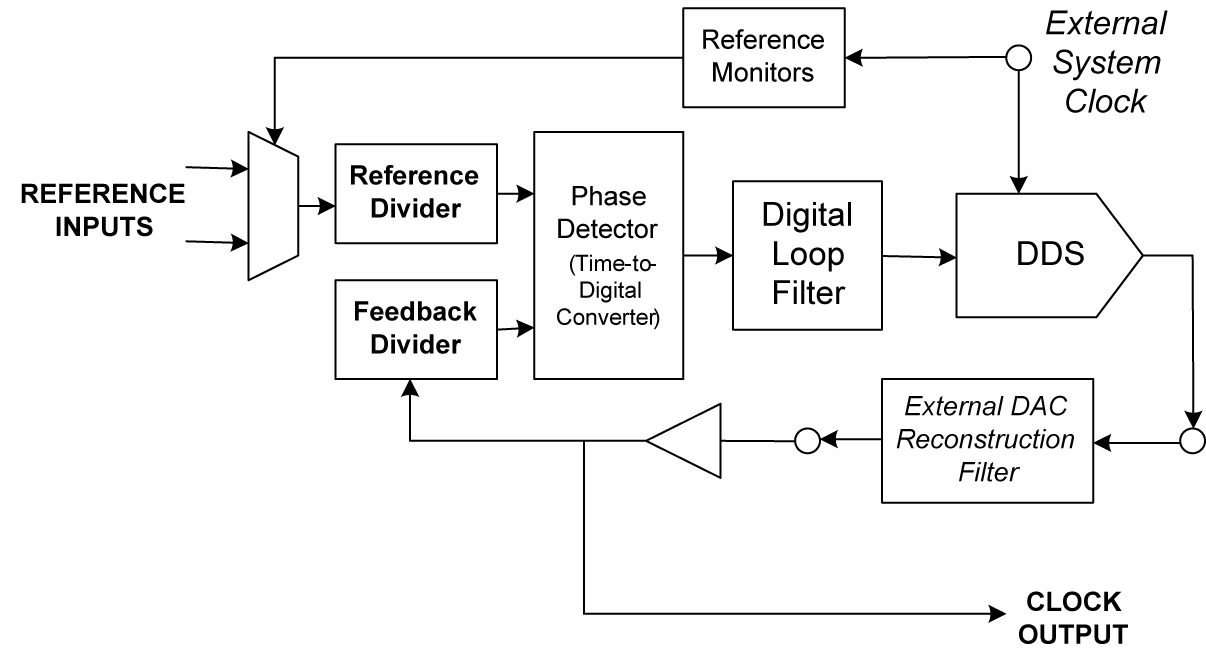

圖2 基于DDS的數字PLL結構框圖

圖中:REFERENCE INPUT-參考輸入;Reference Divider-參考分頻器;Feedback Divider-反饋分頻器;Phase Detector (Time-to-Digital Converter) -鑒相器(時間數字轉換器);Reference Monitors-參考監控器;Digital Loop Filter-數字環路濾波器;External System Clock-外部系統時鐘;External DAC Reconstruction Filter-外部DAC重構濾波器;CLOCK OUTPUT-時鐘輸出

在基于DDS的數字PLL中,直接數字頻率合成(DDS)和數模轉換器(DAC)代替了傳統的壓控振蕩器(VCO)。DDS的輸入是數字調諧字,用于設置輸出信號的頻率。這與VCO類似,VCO的模擬輸入電壓用于調節輸出信號的頻率。在1GHz頻率下運行的DDS的調諧頻率范圍為DC~400MHz。如果利用奈奎斯特頻率(DAC采樣速率的一半)以上的DAC鏡像作為信號,頻率范圍還可以進一步增大。DAC的輸出被送到外部低通重構濾波器中,以濾除不需要的諧波,然后再反饋到內置反饋分頻器中,這樣就形成了閉合回路。

數字PLL中的重構濾波器是模擬PLL中沒有的部分。低通濾波器濾除基頻頻率以上的頻率信號。根據濾波需求以及輸出頻率與奈奎斯特頻率的接近程度,通常會采用五階或七階低通濾波器。之后,正弦波被送入扇出緩沖器中,以產生方波時鐘輸出信號。為了濾除附加噪聲或允許PLL工作于奈奎斯特頻率以上,可使用帶通濾波器代替低通濾波器。這時有可能在輸出頻率或低于輸出頻率的地方出現沒有濾除的雜散,因此設計者必須謹慎做出頻率規劃,在不會出現問題的頻率上運行DAC。

一旦理解了數字PLL中的各個組成模塊,我們就能夠開始認識到與這些數字單元相關的優勢。首先,數字PLL非常適合頻率轉換應用。例如,將普通的19.44MHz的時鐘頻率轉換為156.25MHz,需要對輸入信號進行1944分頻,使鑒相器在10kHz頻率下工作。為了保持環路的穩定性, PLL環路帶寬通常被限制在鑒相器頻率的1/10左右,在本例中帶寬為1kHz。小數N分頻PLL有助于保持鑒相器的高工作頻率,但會帶來自身的一些問題。在模擬PLL中,低環路帶寬需要大容量的元件,這不僅會占用電路板空間,而且當使用陶瓷電容時還會導致自諧振。由于相位修正的步長有限,數字PLL也可能產生參考雜散信號,但是,由于數字環路濾波器很容易實現非常小的環路帶寬(< 1 Hz),因此這個雜散信號很容易被抑制。更重要的是,由于環路特性由數字系數來決定,因此數字PLL能夠比模擬PLL更好地控制環路動態特性。這是相位調制系統的一個主要優點。

對任何PLL來說,PLL環路帶寬內的參考噪聲能通過,而帶外的參考噪聲會被衰減。基于DDS的雙環路數字PLL架構的主要優點是輸出相位噪聲取決于DAC系統時鐘,而不是模擬VCO。這允許設計人員選擇能夠滿足其特定抖動需求的系統時鐘源。在模擬PLL中,用其它VCO取代現有VCO需要匹配供電電壓、增益、頻率范圍以及其它參數,這是很困難的,但并不是不可能的。在模擬PLL中,設計人員必須為了VCO相位噪聲而對VCO調諧范圍進行權衡,VCO噪聲會隨著VCO頻率范圍的增加而增加。而DDS數字PLL就沒有這樣的限制。通過提供一個干凈的DAC系統時鐘,設計人員可以獲得等效的寬帶低噪聲VCO。設計人員可以選擇低的PLL環路帶寬以清除抖動。如何選擇合適的DAC系統將在下文中介紹。

由于數字PLL中的鑒相器增益、環路帶寬和相位裕度都是可編程的,因此用戶可以在不同的條件下保持相同的環路傳遞函數。例如,為吉比特以太網產生125MHz的參考時鐘,參考輸入信號可能是8kHz的BITS時鐘,也可能是19.44MHz的SONET/SDH參考時鐘。在這兩種情況下,數字PLL中為獲得固定的環路帶寬和相位裕度,可對環路濾波器進行優化。更重要的是,只需對寄存器進行編程就可以調整環路參數,而無需更換器件。

基于DDS的數字PLL的另一個重要優點就是可以使用高速DAC系統時鐘來進行參考監控。此時鐘可用來對參考輸入信號進行過采樣,允許對參考時鐘的漂移或故障進行快速檢測。一旦檢測到故障,設備或者自動切換輸入信號,或者轉入保持模式。在數字邏輯中能夠很容易地實現時鐘無中斷切換。當兩個參考時鐘都發生故障時,就會出現時鐘保持,并且如果需要,數字PLL就會像一個DDS頻率合成器一樣連續輸出相同頻率的信號。在保持模式下,輸出時鐘的穩定性與系統時鐘相同。如果要利用模擬PLL實現這一功能,那么則需要一個與參考輸入信號頻率成倍數的外部振蕩器,或者需要VCO的控制電壓在長時間內及一定溫度下是穩定的亞微伏電平。前者也許可行,而后者一定無法實現。

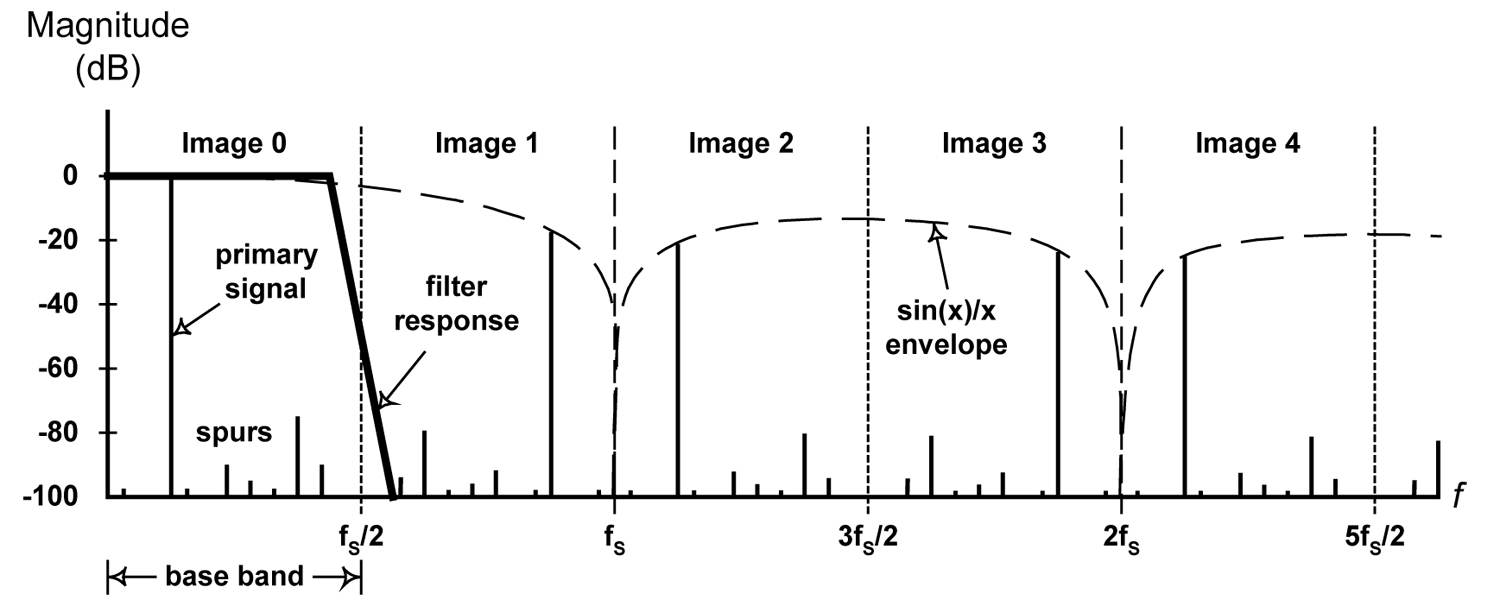

DAC雜散的存在是數字PLL的一個缺點。這里只對DAC雜散做簡要的介紹。即使是理想的DAC,也會在整個頻帶內產生諧波和不希望的譜能量,這是由DAC的非線性特性造成的。DAC性能的衡量標準是在沒有重構濾波器的情況下測得的無雜散動態范圍(SFDR)。SFDR是從直流到DAC采樣頻率一半范圍內最大雜散與載波功率值的比值。對于14bit DAC來說,寬帶SFDR通常為-50dBc ~ -70dBc。在希望的輸出頻率處或輸出頻率之下出現高階的DAC雜散是有可能的,這些雜散的幅值通常很低(< 70 dBc)。衰減DAC雜散的主要方法是使用重構濾波器,七階的低通濾波器可以快速地削弱雜散信號。圖3所示的是典型的DAC輸出頻譜和重構濾波器頻率響應。設計人員應該謹慎地選擇系統的時鐘頻率,使低階的雜散信號不會與希望的輸出頻率太接近,從而有效地濾除雜散。

圖3 DAC的頻譜與重構濾波器響應的關系

圖中:Magnitude-幅值;Image-鏡像;primary signal-主信號;filter response-濾波器響應;envelope-包絡;spurs-雜散;base band-基帶

使用數字PLL時,選擇合適的DAC系統時鐘是很重要的。在大多數應用中,高頻振蕩器可用于直接提供800MHz ~ 1000MHz的DAC系統時鐘。但是,這些器件比較昂貴,很少會使用。而許多數字PLL具有模擬PLL時鐘倍頻器,其產生的相位噪聲在許多應用中也是可以接受的。這樣,設計人員可以使用通用的16MHz或25MHz晶體或頻率范圍在16MHz ~ 100MHz的晶體振蕩器,通過片上PLL產生1GHz的系統時鐘。在計算任何抖動時,都必須考慮片上PLL的噪聲。

選擇晶體振蕩器時,設計人員應該考慮希望的輸出相位噪聲及穩定性的需求。例如,如果在保持模式下需求Stratum 2的時鐘穩定度,那么,就應該為系統時鐘使用Stratum 2兼容的振蕩器。輸出相位噪聲不僅是振蕩器相位噪聲的函數,而且包括由系統時鐘PLL(如果使用的話)提供的倍頻量。采用80MHz的三階泛音晶體振蕩器驅動系統時鐘PLL時得到的總相位噪聲,會優于采用25MHz振蕩器驅動時所得到的總相位噪聲。

為了克服任何一種PLL設計的限制,可以使用數字PLL結合模擬PLL的解決方案。數字PLL能夠處理時鐘切換和頻率比的問題,而模擬PLL則用來進一步衰減雜散,增大頻率,并進行時鐘分配。

那么模擬PLL和數字PLL哪個更好呢?當然,答案取決于具體的應用。在不需要保持、參考切換和環路配置的系統中,模擬PLL是更好的解決方案,且允許產生較高的輸出頻率。而在需要流暢切換、保持,及較好控制環路動態范圍的冗余時鐘應用中,數字PLL是更好的解決方案。它的靈活性和動態配置能力允許參考輸入可以是不同頻率,而且,基于DDS的數字PLL允許參考頻率很低。

基于DDS的數字PLL能提供傳統PLL不能實現的解決方案。通過應用數字邏輯實現PLL構建模塊,性能與靈活性都得到提升,比模擬PLL更具吸引力。

本文作者:

Paul Kern 現任ADI公司時鐘與信號合成部時鐘應用工程師。Paul獲得美國加利福尼亞圣克拉拉大學電子工程學士和碩士學位。

評論