- include timescale.v// synopsys translate_on`include can_defines.v module can_top( `ifdef CAN_WISHBONE_IF wb_clk_i, wb_rst_i, wb_dat_i, wb_dat_o, wb_cyc_i, wb_stb_i, wb_we_i,

- 關鍵字:

代碼 分析 IP 控制器 總線 CAN

- 一、全面認識高清1.1高清不僅僅是高清IP,還有數字高清、模擬高清。高清IP從感光器件上又可分為...

- 關鍵字:

高清 IP

- 工業和信息化部等七部門發布了關于推進光纖寬帶網絡建設的意見>>,計劃到2011年光纖寬帶端口達到8000萬個,城市用戶的接入能力平均達到8Mbit/s以上,農村用戶的接入能力平均達到2Mbit/s以上,商業樓宇用戶基本達到

- 關鍵字:

骨干網 轉型 傳輸 和光 IP 融合

- 恩智浦半導體NXP Semiconductors N.V. (NASDAQ:NXPI) 今日宣布將以開源授權方式提供其JenNet-IP超低功耗IEEE 802.15.4無線連接網絡層軟件,作為其“物聯網”實施計劃的一部分。近年來,人們對物聯網的興趣與日俱增,在物聯網中,每臺設備都有一個IP地址,可以通過安全互聯網連接進行監視和控制。然而,物聯網普及所面臨的主要障礙是不同應用都有不同的網絡軟件。通過發布基于開源授權的JenNet-IP網絡層軟件,并為眾多開發者和用戶提供支持,恩智浦志在簡化為多種設備添加“

- 關鍵字:

恩智浦 JenNet-IP

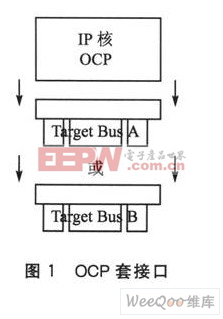

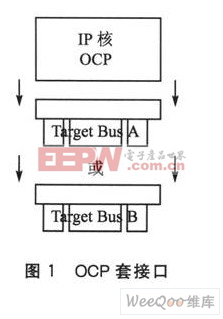

- 基于OCP-IP的SOC總線即插即用的實現,本文討論了OCP-IP的協議與特點,設計了基于AMBA總線的OCP-IP接口,提出了一種IP自動封裝的方法,為IP核的集成和管理帶來極大的方便。

- 關鍵字:

實現 總線 SOC OCP-IP 基于

- 由于移動智能終端的成熟、HSPA的規模商用和無線數據業務資費的下降,移動對固定業務的替代也從語音蔓延到...

- 關鍵字:

LTE 移動寬帶 IP RAN 智能終端

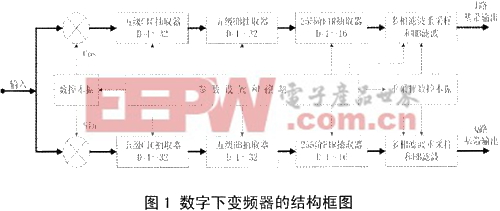

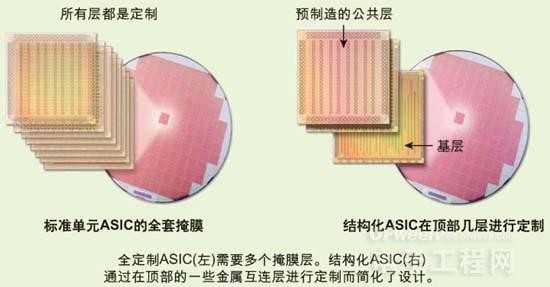

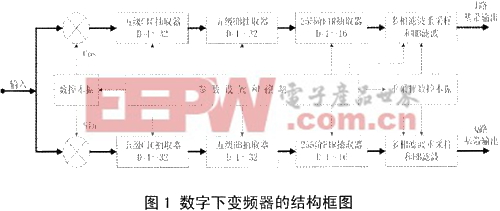

- 數字下變頻(DDC)中坐標變換模塊的ASIC實現,數字下變頻器中坐標變換模塊的ASIC實現1.引言

數字下變頻(DDC)技術是軟件無線電接收機的核心技術。其基本功能是從輸人的寬帶高速數字信號中提取所需的窄帶信號,將其下變頻為數字基帶信號,并轉換成較低的數據率

- 關鍵字:

模塊 ASIC 實現 變換 坐標 變頻 DDC 數字

- 如何更大發揮展會對珠三角電子產業和中國創新的推動作用,這一問題一直困擾著深圳市半導體行業協會秘書長蔡錦江。自去年將“泛珠三角集成電路產品展示暨高峰論壇”系列活動升級為“深圳集成電路創新應用展”獲得成功之后,作為會議組織機構,他和他的團隊就在積極思索這個問題。

“電子產業正在發生巨大的變化,創新的動力和方式也在不斷變遷,我們要及時把握這些趨勢,找到準確的展會定位,更好地幫助珠三角乃至全中國的電子制造企業實現從‘中國制造&rsq

- 關鍵字:

IC設計 IP

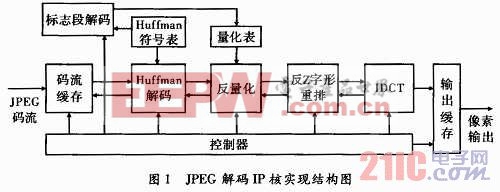

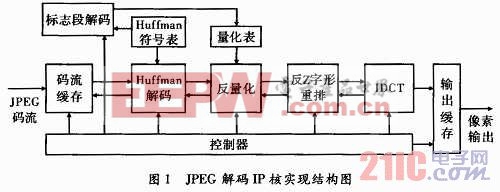

- 摘要:介紹了基于靜止圖像壓縮標準JPEG解碼器IP核的設計與實現。設計采用適于硬件實現的IDCT算法結構,通過增加運算并行度和流水線技術相結合的方法以提高處理速度。根據Huffman碼流特點,采用新的Huffman并行解碼硬

- 關鍵字:

實現 設計 IP 解碼器 JPEG

- 摘要:時鐘樹綜合是當今集成電路設計中的重要環節,因此在FFT處理器芯片的版圖設計過程中,為了達到良好的布局效果,采用時序驅動布局,同時限制了布局密度;為了使時鐘偏移盡可能少,采用了時鐘樹自動綜合和手動修改

- 關鍵字:

ASIC 后端設計 時鐘樹

- 全球領先的半導體設計、驗證和制造軟件及知識產權(IP)供應商新思科技有限公司(Synopsys, Inc., 納斯達克股票市場代碼:SNPS)日前宣布推出動態解析度自適應(DRA)解碼器軟件的優化版本,主要面向已廣泛應用的DesignWare? ARC? Sound AS211SFX 和各種AS221BD 音頻處理器。

- 關鍵字:

Synopsys DRA IP

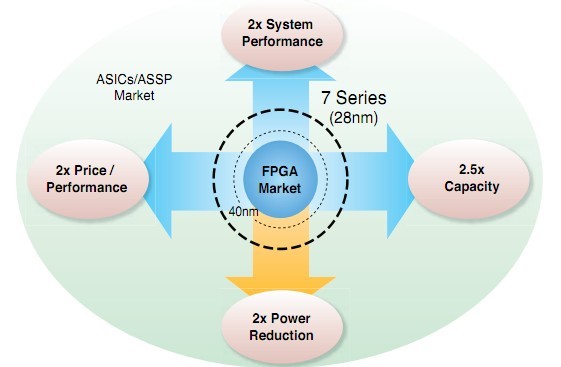

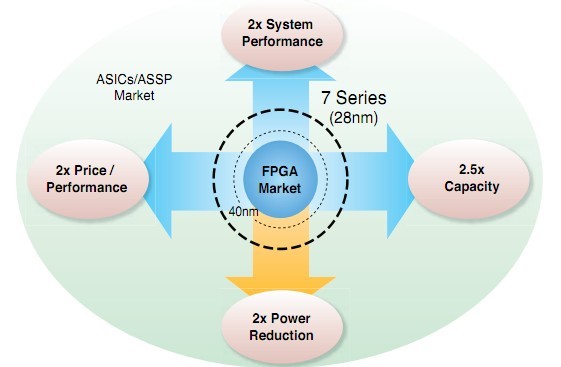

- 日前, 全球可編程平臺領導廠商賽靈思公司 (Xilinx, Inc. (NASDAQ:XLNX))宣布,為建立新的 FPGA 應用市場, 賽靈思公司將通過其開放式平臺以及對業界重要標準的支持變革生態系統, 推動賽靈思聯盟計劃向縱深層次發展。作為該計劃的一部分, 賽靈思將幫助 FPGA 用戶根據其具體的設計與開發要求更方便快捷地找到理想的合作伙伴, 同時提升客戶與賽靈思聯盟計劃成員合作時的滿意度和質量。

賽靈思合作伙伴生態系統及聯盟高級總監 Dave Tokic 指出: “客戶開始越來

- 關鍵字:

Xilinx ASIC ASSP

- 自上世紀80年代中期FPGA作為1,500 ASIC等效門器件首次進入市場以來,FPGA已經取得了長足的發展。二十年后,隨著賽靈思新款7系列的推出,FPGA準備實踐其曾經的承諾,即在某天完全取代ASIC,成為電子行業的主流邏輯IC。隨著7系列FPGA的推出,通過更低的傳統上由ASIC和ASSP占據主要地位的中低批量應用市場的總擁有成本,同時為大批量應用市場提供等同的總擁有成本,賽靈思進而從PLD生產商搖身一變成為了一流的邏輯IC供應商。另外,這種總擁有成本上的優勢與傳統上FPGA能夠加速產品面市和降低

- 關鍵字:

Xilinx 28nm ASIC ASSP

asic ip介紹

您好,目前還沒有人創建詞條asic ip!

歡迎您創建該詞條,闡述對asic ip的理解,并與今后在此搜索asic ip的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473