ASIC后端設計中的時鐘樹綜合

摘要:時鐘樹綜合是當今集成電路設計中的重要環節,因此在FFT處理器芯片的版圖設計過程中,為了達到良好的布局效果,采用時序驅動布局,同時限制了布局密度;為了使時鐘偏移盡可能少,采用了時鐘樹自動綜合和手動修改相結合的優化方法,并提出了關于時鐘樹約束文件的設置、buffer的選型及手動修改時鐘樹的策略,最終完成了FFT處理器芯片的時鐘樹綜合并滿足了設計要求。

關鍵詞:FFT處理器芯片;布局布線;時鐘樹綜合;時鐘偏移

0 引言

在大規模高性能的ASIC設計中,對時鐘偏移(Clock Skew)的要求越來越嚴格,時鐘偏移是限制系統時鐘頻率的主要因素。而時鐘樹綜合又是減小時鐘偏移的有效途徑,因此它是ASIC后端設計中最重要的環節之一。本文以基于SOC Encounter,采用SMIC0.18μm工藝進行的FFT處理器的版圖設計為例,提出在設計過程中如何減小時鐘偏移,結合手動優化幫助工具設計出更好的時鐘樹。

1 時鐘偏移產生的原因分析

同一時鐘源到達各個同步單元的最大時間差稱作時鐘偏移。產生時鐘偏移的原因有:時鐘源到各個時鐘端點的路徑長度不同;各個端點負載不同;在時鐘網中插入的緩沖器不同等。時鐘偏差過大會引起同步電路功能混亂。

在圖1中,假設CLK到達reg1和reg2的時間差最大,為dskew,組合邏輯C的延時為dc,寄存器的延時為d,其建立時間約束為dsetup,保持時間為dhold,時鐘周期為T。滿足建立時間的要求是在CLK2跳變前的dsetup時間,reg2上D端的數據應該穩定,考慮最壞情況reg1比reg2晚dskew,這時滿足的時間關系應該是:

![]()

滿足保持時間的要求是:在CLK2跳變后的dhold時間內,reg2上D端的數據必須保持穩定,考慮最壞情況reg1比reg2早dskew,這時滿足的時間關系應該是:

![]()

由此可見,時鐘偏移對電路速度和時鐘頻率的限制是很大的,而寄存器的保持時間、建立時間和自身的延時,都是與器件單元本身的結構和性質有關,依賴于工藝的改進來進一步減小,所以減小skew成為后端設計重要內容,也是提高電路速度的關鍵。

2 SOC Encounter的時鐘樹綜合

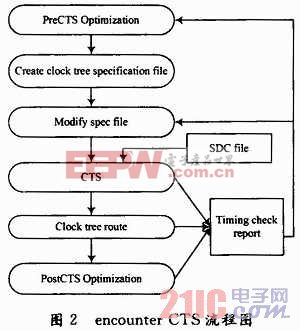

SOC Encounter的時鐘樹綜合在完成布局之后進行,可以采用手動模式和自動模式。手動模式能控制時鐘樹的層次、buffer的數目和每層加入buffer的類型。自動模式根據時鐘樹定義文件自動決定時鐘樹的層次和buffer的數目。時鐘樹綜合從外部時鐘輸入端口自動遍歷整個時鐘樹,遍歷完成后加入buffer用來平衡時鐘樹。SOC Encounter的時鐘樹綜合流程如圖2所示。

評論