3月31日消息,據媒體報道,位于新竹和高雄的兩大臺積電工廠將是2nm工藝制程的主要生產基地,預計今年下半年正式進入全面量產階段。在前期試產中,臺積電已經做到了高達60%的良率表現,待兩大工廠同步投產之后,月產能將攀升至5萬片晶圓,最大設計產能更可達8萬片。與此同時,市場對2nm芯片的需求持續高漲,最新報告顯示,僅2025年第三、四季度,臺積電2納米工藝即可創造301億美元的營收,這一數字凸顯先進制程在AI、高性能計算等領域的強勁需求。作為臺積電的核心客戶,蘋果將是臺積電2nm工藝制程的首批嘗鮮者,預計iP

關鍵字:

臺積電 2nm 量產 蘋果首發 晶圓 GAAFET架構 3nm FinFET

在上周的VLSI研討會上,英特爾詳細介紹了制造工藝,該工藝將成為其高性能數據中心客戶代工服務的基礎。在相同的功耗下,英特爾 3 工藝比之前的工藝英特爾 4 性能提升了 18%。在該公司的路線圖上,英特爾 3 是最后一款使用鰭片場效應晶體管 (FinFET) 結構的產品,該公司于 2011 年率先采用這種結構。但它也包括英特爾首次使用一項技術,該技術在FinFET不再是尖端技術之后很長一段時間內對其計劃至關重要。更重要的是,該技術對于該公司成為代工廠并為其他公司制造高性能芯片的計劃至關重要。它被稱為偶極子功

關鍵字:

英特爾 FinFET 代工計劃

這款測試芯片是業界首款采用12納米FinFet(FF)技術為音頻IP提供完整解決方案的產品。該芯片完美結合了高性能、低功耗和優化的占板面積,為電池供電應用提供卓越的音質與功能。這款專用測試芯片通過加快產品上市進程、提供同類最佳性能、及確保穩健的產品設計,堅定客戶對Dolphin Design產品的信心,再度證實了Dolphin Design在混合信號IP領域的行業領先地位。2024年2月22日,法國格勒諾布爾——高性能模擬、混合信號、處理知識產權(IP)以及ASIC設計的行業領先供應商Dolphin De

關鍵字:

Dolphin Design 12納米 12nm FinFet 成功流片

3D 芯片堆疊對于補充晶體管的發展路線圖至關重要。

關鍵字:

FinFET

摘要:●? ?全新參考流程針對臺積公司 N4PRF 工藝打造,提供開放、高效的射頻設計解決方案。●? ?業界領先的電磁仿真工具將提升WiFi-7系統的性能和功耗效率。●? ?集成的設計流程提升了開發者的生產率,提高了仿真精度,并加快產品的上市時間。近日宣布,攜手是德科技(Keysight)、Ansys共同推出面向臺積公司業界領先N4PRF工藝(4納米射頻FinFET工藝)的全新參考流程。該參考流程基于新思科技的定制設計系列產品,為追求更高預測精度

關鍵字:

新思科技 是德科技 Ansys 臺積公司 4 納米 射頻 FinFET 射頻芯片設計

●? ?新參考流程采用臺積電 N4PRF 制程,提供了開放、高效的射頻設計解決方案●? ?強大的電磁仿真工具可提升 WiFi-7 系統的性能和功率效率●? ?綜合流程可提高設計效率,實現更準確的仿真,從而更快將產品推向市場是德科技、新思科技和Ansys攜手為臺積電的先進4nm射頻FinFET制程打造全新參考流程,助力RFIC半導體設計加速發展是德科技、新思科技公司和 Ansys 公司近日宣布攜手推出面向臺積電 N4PRF 制程的新參考流程。N4P

關鍵字:

是德科技 新思科技 Ansys 臺積電 4nm射頻 FinFET

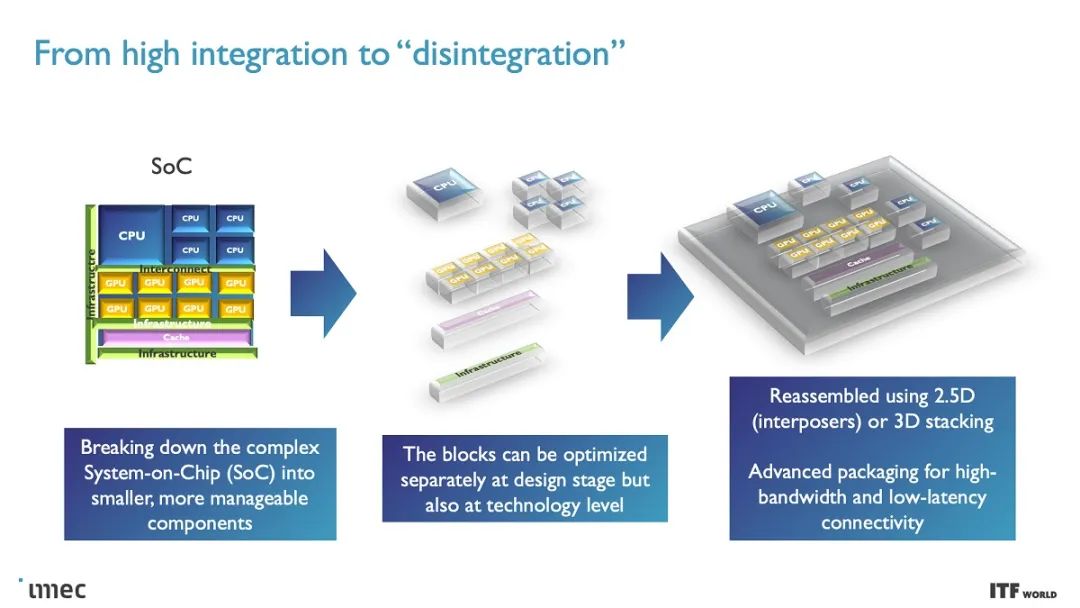

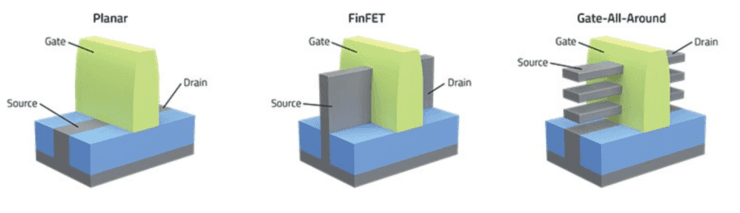

近日,比利時微電子研究中心(IMEC)發表1納米以下制程藍圖,分享對應晶體管架構研究和開發計劃。外媒報導,IMEC制程藍圖顯示,FinFET晶體管將于3納米到達盡頭,然后過渡到Gate All Around(GAA)技術,預計2024年進入量產,之后還有FSFET和CFET等技術。△Source:IMEC隨著時間發展,轉移到更小的制程節點會越來越貴,原有的單芯片設計方案讓位給小芯片(Chiplet)設計。IMEC的制程發展愿景,包括芯片分解至更小,將緩存和存儲器分成不同的晶體管單元,然后以3D排列堆疊至其

關鍵字:

IMEC 1nm 制程 FinFET

● 恩智浦和臺積電聯合開發采用臺積電16納米FinFET技術的嵌入式MRAM IP● 借助MRAM,汽車廠商可以更高效地推出新功能,加速OTA升級,消除量產瓶頸● 恩智浦計劃于2025年初推出采用該技術的新一代S32區域處理器和通用汽車MCU首批樣品 荷蘭埃因霍溫——2023年5月22日——恩智浦半導體(NXP Semiconductors N.V.,納斯達克股票代碼:NXPI)近日宣布與臺積電合作交付行業首創的采用16納米

關鍵字:

恩智浦 臺積電 FinFET 嵌入式MRAM

意法半導體(ST)和GlobalFoundries (GF)剛剛簽署了一份諒解備忘錄,將在意法半導體位于法國Crolles的現有晶圓廠旁邊新建一座聯合運營的300毫米半導體晶圓廠。新工廠將支持多種半導體技術和工藝節點,包括FD-SOI。ST和GF預計,該晶圓廠將于2024年開始生產芯片,到2026年將達到滿負荷生產,每年生產多達62萬片300毫米晶圓。法國東南部的Crolles,距離意大利邊境不遠,長期以來一直是FD-SOI發展的溫床。從許多方面來看,FD-SOI是一種技術含量較低的方法,可以實現FinF

關鍵字:

FD-SOI GAAFET FinFET

英特爾近期于美國檀香山舉行的年度VLSI國際研討會,公布Intel 4制程的技術細節。相較于Intel 7,Intel 4于相同功耗提升20%以上的效能,高效能組件庫(library cell)的密度則是2倍,同時達成兩項關鍵目標:它滿足開發中產品的需求,包括PC客戶端的Meteor Lake,并推進先進技術和制程模塊。 英特爾公布Intel 4制程的技術細節。對于英特爾的4年之路,Intel 4是如何達成這些效能數據? Intel 4于鰭片間距、接點間距以及低層金屬間距等關鍵尺寸(Critic

關鍵字:

Intel 4 制程技術 FinFET Meteor Lake

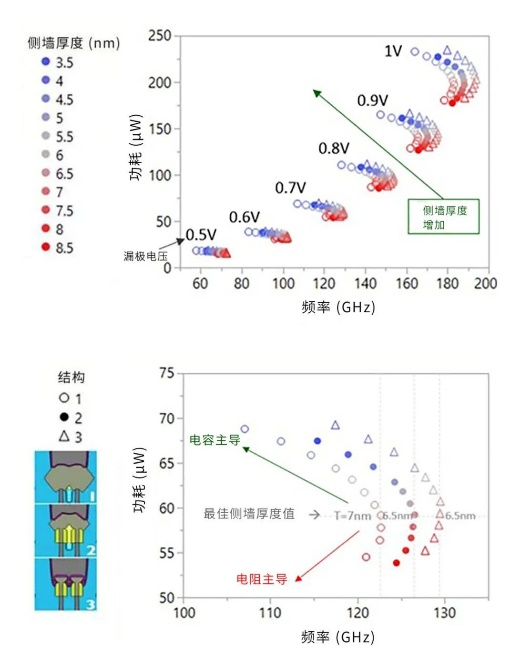

雖然柵極間距(GP)和鰭片間距(FP)的微縮持續為FinFET平臺帶來更高的性能和更低的功耗,但在5nm及更先進節點上,兼顧寄生電容電阻的控制和實現更高的晶體管性能變得更具挑戰。泛林集團在與比利時微電子研究中心 (imec) 的合作中,使用了SEMulator3D?虛擬制造技術來探索端到端的解決方案,運用電路模擬更好地了解工藝變化的影響。我們首次開發了一種將SEMulator3D與BSIM緊湊型模型相耦合的方法,以評估工藝變化對電路性能的影響。這項研究的目的是優化先進節點FinFET設計的源漏尺寸和側墻厚

關鍵字:

泛林 5nm FinFET

觀察2021年主導半導體產業的新技術趨勢,可以從新的半導體技術來著眼。基本上半導體技術可以分為三大類,第一類是獨立電子、計算機和通訊技術,基礎技術是CMOS FinFET。在今天,最先進的是5奈米生產制程,其中有些是FinFET 架構的變體。這是大規模導入極紫外光刻技術,逐步取代多重圖形光刻方法。 圖一 : 半導體的創新必須能轉化為成本可承受的產品。我們知道,目前三星、臺積電和英特爾等主要廠商與IBM 合作,正在開發下一代3/2奈米,在那里我們會看到一種新的突破,因為他們最有可能轉向奈米片全環繞

關鍵字:

CMOS FinFET ST

中芯國際聯席CEO趙海軍透露了公司的先進工藝的情況,表示FinFET工藝已經達產,每月1.5萬片,客戶不斷進來。在最近的財報電話會上,中芯國際聯席CEO趙海軍透露了公司的先進工藝的情況,表示“我們的FinFET工藝已經達產,每月1.5萬片,客戶多樣化,不同的產品平臺都導入了。(這部分)產能處于緊俏狀態,客戶不斷進來。”根據之前的報道,中芯國際的FinFET工藝有多種類型,其中第一代FinFET工藝是14nm及改進型的12nm,目前1.5萬片產能的主要就是14/12nm工藝,第二代則是n+1、n+2工藝,已

關鍵字:

中芯國際 FinFET

finfet+介紹

您好,目前還沒有人創建詞條finfet+!

歡迎您創建該詞條,闡述對finfet+的理解,并與今后在此搜索finfet+的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473