萊迪思 文章 進入萊迪思技術社區(qū)

萊迪思推出適用于SERDES 和視頻時鐘分配的開發(fā)平臺

- 萊迪思半導體公司今日發(fā)布ispClock 5400D 可編程時鐘器件的評估板,價格為169美元。這款新的評估板是適用于ispClock5400D差分時鐘分配器件的評估和設計的易于使用的開發(fā)平臺。該款評估板還可以用于查看5400D器件的性能和在系統(tǒng)編程,或者用作LatticeECP3™ FPGA串行協(xié)議或視頻協(xié)議評估板的副板或時鐘源。 通常,只有帶有LVDS或LVPECL接口的價格昂貴的振蕩器才可用作FPGA SERDES接口應用的參考時鐘源。而現(xiàn)在ispClock5400D器件提供超

- 關鍵字: 萊迪思 開發(fā)平臺 LatticeECP3

為FPGA軟處理器選擇操作系統(tǒng)(08-100)

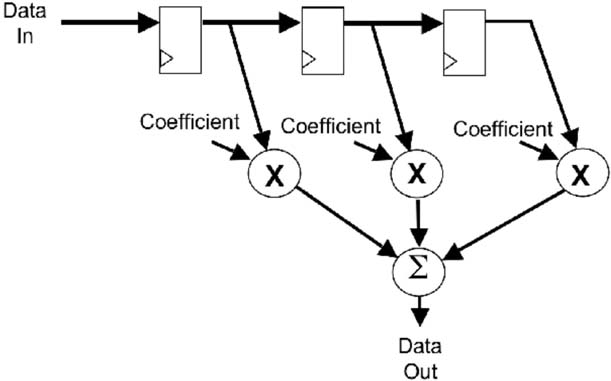

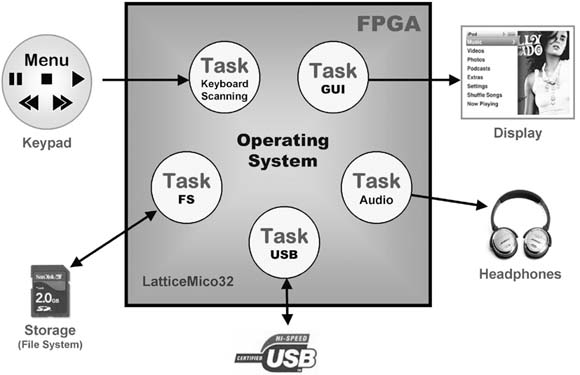

- 操作系統(tǒng)能夠提高可移植性,并提供多種經過測試的抽象層,服務層和應用模塊層以供選擇,從而加快產品上市時間并減少應用程序出錯的可能性。然而,選擇一個嵌入式操作系統(tǒng)( OS )從來就不是一個簡單的過程,因為集成嵌入式軟件的方式選擇余地很大,你可以完全都由自己來編寫,或通過商業(yè)定制專門實時操作系統(tǒng),也可以直接購買通用操作系統(tǒng)不作任何修改,現(xiàn)成的通用操作系統(tǒng)。FPGA性能的提高和軟處理器核的出現(xiàn),直接導致了可編程邏輯SoC解決方案的產生,隨著這一變化,關于選擇標準,設計方案以及折中考慮等傳統(tǒng)經驗也需要與時俱進以

- 關鍵字: 萊迪思 FPGA 操作系統(tǒng)

萊迪思為LatticeECP2低成本FPGA擴展市場

- --第二代 EConomy Plus器件降低了50%的價格并達到雙倍的密度 -- 萊迪思半導體公司近日公布了其第二代EConomy Plus 現(xiàn)場可編程門陣列 (FPGA)器件,LatticeECP2系列。用了富士通90納米CMOS工藝和300毫米硅片,在大批量的情況下,此系列使得FPGA價格降到每1000查找表(LUT)低于0.50美元。與130納米 LatticeECP FPGA相比,新的系

- 關鍵字: LatticeECP2 萊迪思 市場

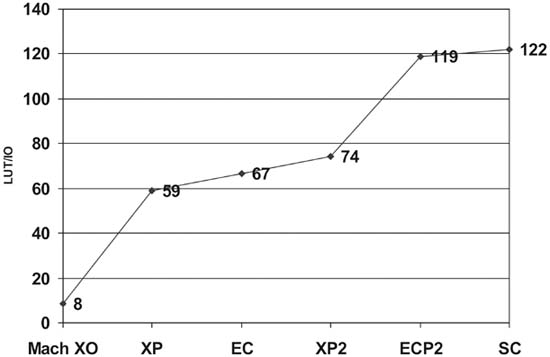

萊迪思富士通發(fā)布LatticeSC和LatticeECP2

- -通力合作打造出難以超越的FPGA產品系列- 萊迪思半導體公司近日宣布推出其新一代的90納米FPGA,包含兩個全新的FPGA器件系列。LatticeSC™ 系統(tǒng)芯片F(xiàn)PGA的設計宗旨是提供業(yè)界最佳的整體性能,而LatticeECP2™ FPGA則將業(yè)界成本最低的FPGA結構和高端的FPGA功能集于一身。這兩個器件系列都采用了富士通公司經過優(yōu)化的工藝,既滿足了高容量FPGA對成本效率的要求,又能夠提供擁有數(shù)百萬門的系統(tǒng)級FPGA所需的千兆赫性能。這兩個器件系列將在

- 關鍵字: LatticeECP2 LatticeSC 富士通 萊迪思

用可編程的扭斜控制來解決時鐘網(wǎng)絡問題的方法

- 時鐘網(wǎng)絡管理問題提高同步設計的整體性能的關鍵是提高時鐘網(wǎng)絡的頻率。然而,諸如時序裕量、信號完整性、相關時鐘邊沿的同步等因素極大地增加了時鐘網(wǎng)絡設計的復雜度。傳統(tǒng)上,時鐘網(wǎng)絡的設計采用了簡單的元件,諸如扇出緩沖器、時鐘發(fā)生器、延時線、零延時緩沖器和頻率合成器。由于PCB走線長度不等而引起的時序誤差,采用蜿蜒走線設計的走線長度匹配方法來處理。走線阻抗與輸出驅動阻抗的不匹配經常通過反復試驗選擇串聯(lián)電阻來消除。多種信號的標準使得時鐘邊沿的同步更加復雜。至今,這三種挑戰(zhàn)會經常遇到,并且鮮有理想的解決方案。以下描述了

- 關鍵字: 萊迪思

可編程邏輯器件融合CPLD+FPGA最佳特性

- 可編程邏輯器件融合CPLD+FPGA最佳特性 Lattice(萊迪思)半導體公司近日推出了新的MachXO可編程邏輯器件系列產品,Lattice稱,這種新一代的跨越式可編程邏輯器件支持傳統(tǒng)上由高密度的CPLD或者低容量的FPGA所實現(xiàn)的應用。 據(jù)Lattice現(xiàn)場應用支持副總裁Jock Tomlinson介紹,MachXO邏輯器件建立在低成本的130nm嵌入式Flash處理工藝上。它能夠在單芯片中瞬時工作,這種特性對于許多CPLD應用來說是十分重要的。3.5ns的管腳至管腳的延時使得器件能夠滿足當代系統(tǒng)

- 關鍵字: Lattice(萊迪思)半導體公司

萊迪思推出ispCLOCKTM高性能時鐘發(fā)生器器件

- 萊迪思半導體公司(NASDAQ:LSCC)今天宣布推出其革命性的ispCLOCKTM在系統(tǒng)可編程時鐘發(fā)生器器件新系列。ispClock5500系列中的第一批器件:10輸出的ispClock5510 和 20 輸出的 ispClock5520將一個高性能的時鐘發(fā)生器和一個靈活的通用扇出緩沖器合成在一起。采用了一個高性能的鎖相環(huán)以及時鐘乘除工具,該片上的時鐘發(fā)生器可以提供多達5個頻率范圍從10MHz到320MHz的時鐘。無論是單端還是差分信號模式,通用扇出緩沖器都可以驅動多達20個時鐘網(wǎng)絡,并且每一個輸出都是

- 關鍵字: 萊迪思

萊迪思推出業(yè)界第一個混合信號PLD、開拓了電源管理市場

- 世界上最大的在系統(tǒng)可編程器件供應商-萊迪思半導體公司(納斯達克代號:LSCC)宣布推出其創(chuàng)新的PowerPAC™器件。這是業(yè)界第一片混合信號可編程邏輯器件(PLD),它內含在系統(tǒng)可編程的模擬和邏輯組塊,能提供經過優(yōu)化的電源管理功能,這一功能對如今的多電源電子系統(tǒng)是至關重要的。該器件集成了可編程邏輯、電壓比較器、參考電壓及高電壓的場效應管驅動器,支持單芯片可編程供電定序與監(jiān)控,為總值達到120億美元的電源半導體市場奉獻了獨特的可編程控制方案。雖然,微處理器、DSP、FPGA和專用集成電路(ASI

- 關鍵字: 萊迪思 模擬IC 電源

萊迪思低功耗的CPLD 器件系列將其可編程解決方案拓展至便攜式電子產品市場

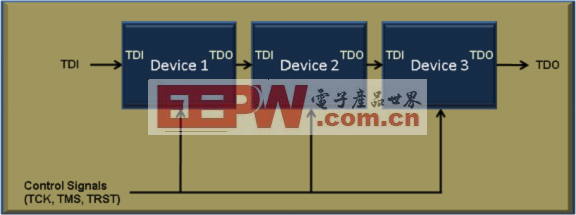

- 在系統(tǒng)可編程(ISP™)邏輯產品的發(fā)明者-萊迪思半導體公司(納斯達克代號:LSCC)今天正式宣布其1.8伏 ispMACH

- 關鍵字: 萊迪思

萊迪思介紹

您好,目前還沒有人創(chuàng)建詞條萊迪思!

歡迎您創(chuàng)建該詞條,闡述對萊迪思的理解,并與今后在此搜索萊迪思的朋友們分享。 創(chuàng)建詞條

歡迎您創(chuàng)建該詞條,闡述對萊迪思的理解,并與今后在此搜索萊迪思的朋友們分享。 創(chuàng)建詞條

相關主題

關于我們 -

廣告服務 -

企業(yè)會員服務 -

網(wǎng)站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司