用PLD簡化邊界掃描測試

引言

本文引用地址:http://www.j9360.com/article/111150.htm隨著JTAG標準IEEE1149.1的定型,及隨后開始在集成電路Intel 80486中采用,邊界掃描測試已被廣泛應用于測試印刷電路板的連接,以及在集成電路內進行測試。邊界掃描測試受到設計人員的歡迎,因為它能夠在線測試,而無需昂貴的釘床在線測試設備。然而,在大的電路板上,邊界掃描鏈路很長,電路板設計人員面臨著多種挑戰,諸如故障檢測和隔離、測試時間、物理布線,同時還要管理偏移,電壓轉換和滿足各種特殊需要。傳統上使用ASSP來應對這些挑戰,然而基于ASSP的解決方案更為昂貴,有固定的電平和一些端口,不允許任何的定制,還要手工干預。本文主要探討如何利用可編程邏輯器件作為一個頗具吸引力的選擇,以解決大的電路板上與邊界掃描測試相關的挑戰。

電路板設計人員面臨的邊界掃描挑戰

在電信和網絡路由設備中使用的那些大的電路板通常包含許多有邊界掃描功能的器件。在這些板上實施邊界掃描測試時,設計人員通常面臨著以下挑戰:

故障檢測/隔離

測試長的掃描鏈路是困難的,因為在一個掃描鏈路上的故障可能會導致整個系統不能進行測試。此外,由于這些器件是處于菊花鏈之中,測試系統以鏈路中最慢的器件的速度運行。 這既增加了測試時間,還增加了成本。

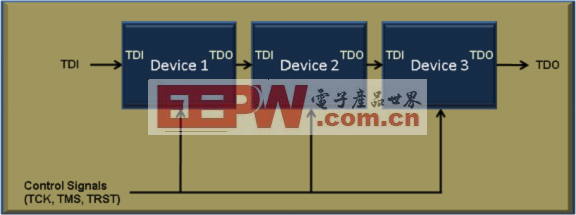

物理布線至平衡時鐘偏移

雖然掃描測試數據端口為菊花鏈輸入,典型的控制信號,如TCK(測試時鐘)TMS (測試模式設置) 和TRST(測試復位) 是直接分配的,從測試端口到掃描鏈路中的每一個器件。圖1展示了邊界掃描測試的一個典型的安排。當掃描鏈中器件的數量增加時可以觀察到偏移的影響。解決這個問題的最常見的方法是要增加緩沖器,以便管理板上的偏移,但是這樣做增加了成本和復雜性。

圖1:典型的邊界掃描鏈路

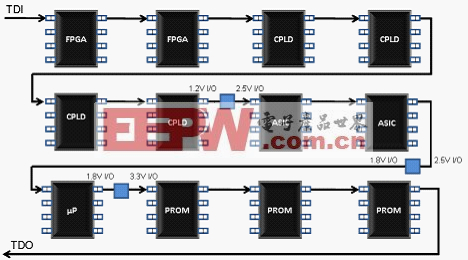

電壓轉換

邊界掃描I / O電壓應該與掃描鏈路中連接器件之間的電壓相兼容。然而,電路板上器件的I / O的信號電平往往是不兼容的。為了解決這個問題,設計人員通常添加電壓轉換器件。圖2展示了這樣一個掃描鏈路,其中元件具有不同的I / O電壓。當一個器件的I / O電壓與鏈路中的下一個器件的I / O電壓不同時,已在掃描鏈路中插入一個電壓轉換器。在這個例子中,根據 I / O的電壓,在掃描鏈路中的器件已放在一起。當器件的I / O電壓不能放在一起時,更多的電壓轉換器可能需要插入到掃描鏈。

圖2:工作在不同I / O電壓的器件的掃描鏈路

評論