多路同步串口的FPGA傳輸實現

—— Design of Multi-channel Synchronous Serial Transmission Base on FPGA

隨著集成電路技術的發展,FPGA和DSP以及ARM以其體積小、速度快、功耗低、設計靈活、利于系統集成、擴展升級等優點,被廣泛地應用于高速數字信號傳輸及數據處理,以DSP+FPGA+ARM的架構組成滿足實時性要求的高速數字處理系統已成為一種趨勢,本文主要研究FPGA在高速多路數據傳輸中的應用。

本文引用地址:http://www.j9360.com/article/94602.htm系統結構

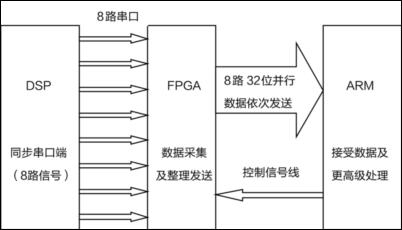

在DSP多路串行數據同時向ARM發送的系統中,因為數據通道有并行要求,應用FPGA硬件并行的特點,由FPGA并行接收多路數據,經過緩沖后再發送至ARM進行數據的高級處理的方案,系統結構圖如圖1所示。

圖1 系統結構圖

FPGA處理模塊實現

DSP的串口傳輸方式為同步串口,每組DSP串口有4個端口,分別為:clk , frame , data_a,data_b[3]。數據端口有兩個,本例中只使能data_a,以下統一稱為data。

DSP同步串口傳輸時序如圖2所示,當frame為1時,串行數據有效,當frame為0時,一幀數據傳輸結束。本例中DSP傳輸的一幀數據為32bit。

圖2 DSP同步串口傳輸時序圖

評論