準諧振反激式電源設計之探討(05-100)

本文引用地址:http://www.j9360.com/article/91455.htm

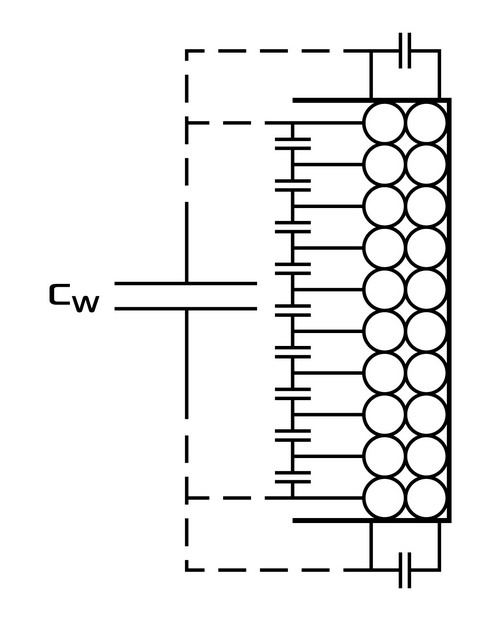

圖2 變壓器的寄生電容

硬開關轉換器中的寄生電容

圖3示出傳統硬開關反激式轉換器。在這種傳統的間斷模式反激式轉換器 (DCM) 的停滯時間期間,寄生電容將與VDC周圍的主要電感發生振蕩。寄生電容上的電壓會隨振蕩而變化,但始終具有相當大的數值。當下一個時鐘周期的MOSFET導通時間開始時,寄生電容 (COSS 和 CW) 會通過MOSFET放電,產生很大的電流尖峰。由于這個電流出現時MOSFET存在一個很大的電壓,該電流尖峰因此會做成開關損耗。此外,電流尖峰含有大量的諧波含量,從而產生EMI。

圖3 硬開關反激式轉換器

準諧振反激式設計的實現

如果不用固定的時鐘來初始化導通時間,而利用檢測電路來有效地“感測”MOSFET (VDS) 漏源電壓的第一個最小值或谷值,并僅在這時啟動MOSFET導通時間,情況又會如何?結果會是由于寄生電容被充電到最小電壓,導通的電流尖峰將會最小化。這情況常被稱為谷值開關 (Valley Switching) 或準諧振開關。在某些條件下,設計人員甚至可能獲得零電壓開關 (ZVS),即當MOSFET被激活時沒有漏源電壓。在這情況下,由于寄生電容沒有充電,因此電流尖峰不會出現。這種電源本身是由線路/荷載條件決定的可變頻率系統。換言之,調節是通過改變電源的工作頻率來進行,不管當時負載或線路電壓是多少,MOSFET始終保持在谷底的時候導通。這類型的工作介于連續 (CCM) 和間斷條件模式 (DCM) 之間。因此,以這種模式工作的轉換器被稱作在邊界條件模式 (BCM) 下工作。

圖4 MOSFET漏-源電壓

準諧振或谷值開關的優勢

在反激式電源設計中采用準諧振或谷值開關方案有著若干優勢。

降低導通損耗

這種設計為設計人員提供了較低的導通損耗。由于FET轉換具有最小的漏源電壓,在某些情況下甚至為零,故可以減小甚至消除導通電流尖峰。這減輕了MOSFET的壓力以及電源的EMI。

降低關斷損耗

準諧振也意味著更小的關斷損耗。由于規定FET會在谷值處進行轉換,在某些情況下,可能會增加額外的漏源電容,以減低漏源電壓的上升速度。較慢的漏源電壓上升時間會減少FET關斷時漏級電流和漏源電壓之間的電壓/電流交迭,使到MOSFET的功耗更少,從而降低其溫度及增強其可靠性。

減少EMI

導通電流尖峰的減小或消除以及較慢的漏源電壓上升速度都會減少EMI。一般而言,這就允許減少EMI濾波器的使用數量,從而降低電源成本。

結語

降低成本和增加可靠性永遠都是電源設計人員的目標。利用準諧振技術可以協助設計人員實現這些目標。準諧振或谷底開關能減輕MOSFET的壓力,從而提高其可靠性。利用準諧振技術,由于波形的諧波含量降低,電源的EMI因此得以減少

評論