數據轉換器串引LVDS接口改善板布線(05-100)

系統往往需要信號傳輸,在信號傳輸中不希望共模信號,共模信號處理困難。某些設計把來自傳感器輸出的單端信號轉換為全差分信號,然后,把此信號送到差分輸出ADC下游。這樣做的優點是在差分線上引起的最大噪聲在兩條線上是共同的(假定差分線是對稱的)。

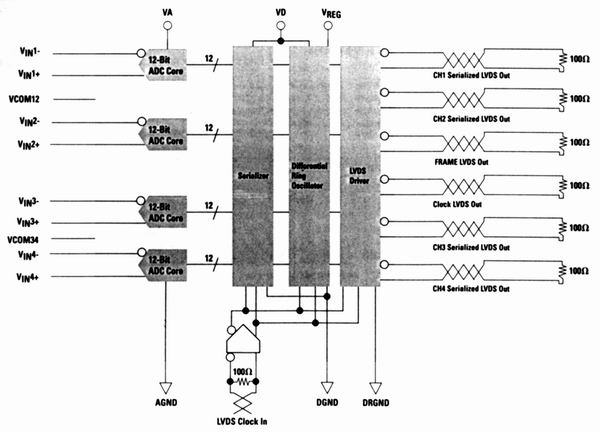

本文引用地址:http://www.j9360.com/article/91453.htm在輸入信號轉換數字數據之后,必須傳輸它們到DSP或ASIC/FPGA進行處理。流行的全差分輸出信號傳輸是方便的。全差分的輸出信號通過兩條對稱線給出和吸收電流。這種信號傳輸的一個例子是LVDS(低壓差分信號)格式。ADC12QS065用LVDS來解決所有這些系統問題(圖1)。

圖1 ADC12QS065簡化框圖

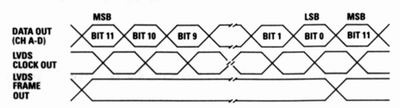

圖2 輸出定時圖

ADC12QS065在單片上包含4個12位ADC。每個ADC輸入都接收全差分信號。輸入共模電壓來源于共模輸出參考電壓VCOM12和VCOM34,由ADC12QS065提供。ADC12QS065可選擇全差分或單端時鐘源。為了采用LVDS,時鐘提供LVDS到CLKB,端接緊靠輸入引腳。若希望單端CMOS時鐘,則把CLKB接低態,而不需要端電阻器。

用差分環形振蕩器串行化每個ADC的輸出。輸入時鐘輸入乘12,并轉換到LVDS時鐘輸出,以使數據捕獲。輸入時鐘率的LVDS FRAME信號也在輸出產生來識別取樣數。

輸出定時為FPGA提供容易的數據捕獲。當取樣數據準備好時,發送輸出FRAME信號。在LVDS CLOCK OUT轉變之后,出現4個輸出通道的每個通道的MSB。LVDS CLOCK OUT 信號從DATA OUT 偏移四分之一周期,以減輕時鐘管理。在CLOCK OUT轉換時捕獲每個數據位。采用LVDS的另一個好處是可以用EIA/TIA568標準的雙絞線發送這些信號。滿足EIA/TIA568標準的雙絞線具有100Ω 特性阻抗。緊靠在一起并承載相反電流的導體產生非常低的輻射。在高SNR要求的場合這是所希望的。

在傳統單端并行CMOS輸出12位ADC中,需要49條(4×12+1)線發送轉換器,輸出到數字處理器。若把輸出位串行化,每個通道有單對差分線。也要說明輸出時鐘和幀信號線。

因為LVDS用來自電源的電流,靠來自LVDS端或其他的“操縱”(steering)電流,所以從電源恒定地吸收電流。這降低了呈現在電源線上的開關轉換負載。此優點使電源線上的電源噪聲比較低,從而減小去耦電容的尺寸并減輕布線要求。

串行LVDS允許更小的封裝,而信號傳輸是非常有效的。然而在很多應用中,低功耗是非常重要的。每個通道節省每毫瓦功率,對于需要幾個數據通道的系統有巨大意義。因此,除靜態驅動器外,ADC12QS0D65具有3個分離電源。可以連接每個電源使其成為單電原ADC或保護分離。分離電源進一步隔離ADC內部電路每部分。分離電源的另一個優點是輸出驅動器電壓可以低到2.5V,以節省功耗。

ADC12QS065也具有自己內部參考供電的能力,允許外部驅動基準。這使多ADC可連組在一起,分別把所有的VRET和VREFN連接在一起。靠保證每個芯片匹配的增益和偏移,可減小系統定標要求。若系統允許差分信號傳輸,用低共模噪聲電感是有益的,可以降低電源瞬變,在輸出線上有低數字輻射。ADC12QS065從模擬輸入、時鐘輸入到串行LVDS輸出,提供全差分轉換。它所具有的分離電源能力允許用于進一步模擬數字域分離,并提供較低的功耗。■ (益林)

雙絞線傳輸器相關文章:雙絞線傳輸器原理

評論