高可靠平臺計算機設計

摘要:闡述了32位嵌入式處理器S698體系架構、功能,SOC設計,著重介紹了S698 IP核在平臺計算中的高可靠設計及在航天領域的廣泛應用。

關鍵詞:S698 IP核;SOC;高可靠平臺計算機;FPGA;航天應用

引言

隨著航天技術的不斷發展,對控制的要求也越來越高,需要具備更高的反應速度和更強的數據處理能力。在航天領域,一旦控制發生錯誤,將會造成難以估計的損失。因此,如何提高控制的可靠性是長期以來的一個重要問題。本文介紹了SOC應用方式的一種實際開發方案,重點討論了平臺計算機的高可靠性的設計和實現方法。

高可靠平臺計算機主要任務

本高可靠平臺計算機主要完成以下主要任務:實時錄取慣性測量儀表輸出的轉動角增量和視速度增量;接收機載導航系統給出的初始位置、速度以及姿態數據;實時接收定位衛星測量數據;實時完成制導、姿控方程的運算,按照控制律及制導律要求,對采集的信息進行變換、綜合,形成控制/制導指令,控制舵機;集成1553B總線通信功能,進行總線通信與控制;4路D/A輸出姿態控制指令;具有8級可屏蔽中斷;通過1553B接口與地面計算機通信,進行信息交換;提供三個帶光電隔離的RS422接口。

平臺計算機采用FPGA + S698 IP核 的方案(簡稱SOC),以歐比特公司的S698 IP核做為主CPU,另外再把1553B總線控制器、VME總線控制器、3個帶FIFO的UART整合在一起。體現了歐比特公司S698 IP核靈活、優越性能。并且支持多操作系統。采用SOC設計節省昂貴的流片費用、增加系統設計的靈活性、方便修改、大大縮短設計開發的周期。

高可靠平臺計算機

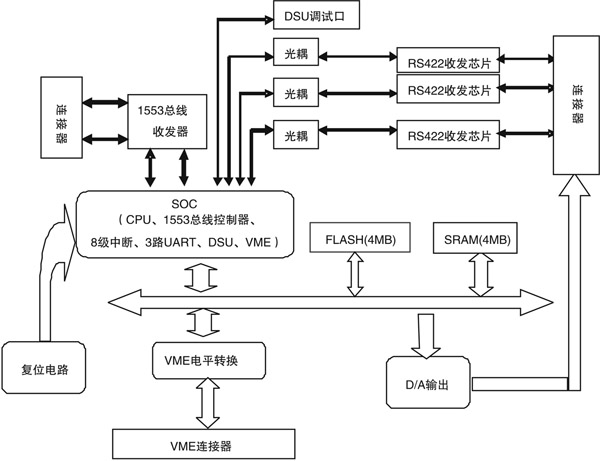

高可靠平臺計算機功能框圖示于圖1。

圖1 高可靠平臺計算機功能框圖

高可靠平臺計算機采用FPGA+S698 IP核的SOC形式實現,FPGA采用ALTERA公司Cyclone系列EP1C20。

高性能的S698 IP核作為內核,集成了大量的外圍設備,并將這些所有的模塊全部集成到一個FPGA器件當中,降低了整個板級系統的成本,縮小了板級系統的體積,器件等級選用工業級以上器件,大大提高了系統的可靠性。

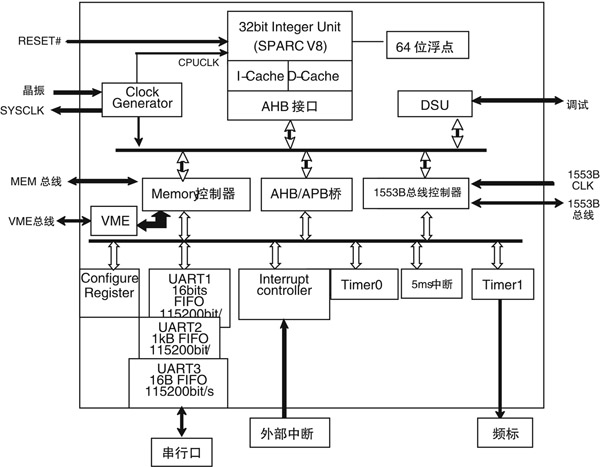

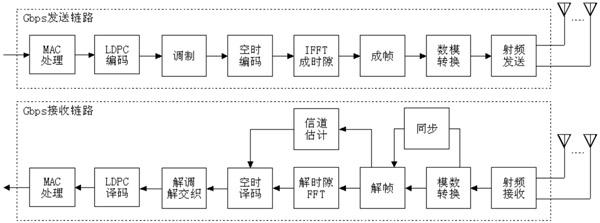

S698 IP核的功能框圖示于圖2。

圖2 S698 IP核功能框圖

S698 IP核特點如下:內部使用了5級流水線,SPARC V8指令集;硬件乘法器和除法器;支持2條DSP指令(MAC & UMAC);浮點運算:雙精度(64位);具有分開的指令和數據cache結構(哈佛結構),可以根據需求靈活的配置cache的容量,大小范圍是1-64kbyte;片上總線規范使用了AMBA2.0規范,支持APB,和AHB標準;外設可裁減,包括UART,定時器,中斷控制器,存儲器管理單元,I/O端口,看門狗等;采用AMBA AHB/APB總線結構的用戶設計新模塊,可以很容易加入到S698 IP核中,完成用戶的定制應用;集成調試支持單元(DSU),支持硬件調試功能。

高可靠平臺計算機系統板具有如下硬件資源:FPGA(集成S698、1553B、VME IP核);1553B部分;VME部分;4MB FLASH;4MB SRAM;4路+10V~-10V,12位DA輸出;3路光電隔離RS422,其中2路具有16字節FIFO,1路1K字節FIFO;頻標頻率可配置;定時器;8級中斷;FPGA提供JTAG、AS接口;1路UART;DSU(硬件調試單元)。

S698 IP核高可靠設計

為了適用于航空航天的高可靠性應用,S698 IP核采用多層次的容錯策略;奇偶校驗、TMR(三模冗余)寄存器、片上EDAC(檢錯和糾錯)、流水線重啟、強迫Cache不命中等。盡管現在幾乎所有CPU都有一些常規的容錯措施,如奇偶校驗、流水線重啟等,像IBM S/390 G5還采用了寫階段以前的全部流水線復制技術。IntelItanium采用的混合ECC和校驗編碼等技術;但遠沒有S698 IP核那樣,采用如此全面的容錯措施。

S698 IP核將時序(存儲)單元的狀態翻轉作為數字容錯的主要內容,根據時序邏輯的不同特點和性質,采用了不同的容錯技術和手段。

1) Cache的容錯。大的Cache對高性能CPU來說是至關重要的,而且位于處理器的關鍵(時間)通路上。為了減少復雜性和時間開銷,錯誤檢測的方法采用2位的奇偶校驗位,l位用作奇校驗,l位偶校驗,因此可以檢查所有的錯誤情況,在讀Cache的同時進行校驗。當校驗出錯誤,強制Cache丟失,并從外部存儲去獲取數據。

2) 處理器寄存器文件的錯誤保護。寄存器文件是處理器內部的寄存器堆,內部的寄存器對于指令的運行速度和用戶程序設計的靈活程度都是很重要的。內部寄存器的使用頻率很大,其狀態的正確性是也很關鍵。S698 IP核采用1、2奇偶校驗位和(32.7)BCH校驗和進行容錯。

3) 觸發器的錯誤保護。處理器的2500個觸發器均采用三模冗余的方式進行容錯,通過表決器來決出正確的輸出。

硬件高可靠設計

3個RS422接口和1553B接口是系統對外接口,RS422采用光電隔離,工作時以光作為媒介來傳遞信息,無觸點,壽命長,響應速度快,輸入和輸出在電氣上是完全隔離的,采用了高等級隔離電源,給光耦單獨供電,抗干擾能力強。

1553B是一種具有可確定性的、傳輸可靠的數據總線,為雙冗余設計,廣泛地應用于不同的軍事平臺(航空系統、地面車輛系統、艦艇系統) 系統,已經發展成國際公認的數據總線標準。

底板數據總線為VME(VersaModule Eurocard),VME總線是一種通用的計算機總線它定義了一個在緊密耦合(closely coupled)硬件構架中可進行互連數據處理、數據存儲和連接外圍控制器件的系統。經過多年的改造升級,VME系統已經發展的非常完善,圍繞其開發的產品遍及了工業控制、軍用系統、航空航天、交通運輸和醫療等領域。

整體的可靠性設計

SPARC 微處理器最突出的特點就是它的可擴展性,這是業界出現的第一款有可擴展性功能的微處理器,它的無窮擴展能力能夠應付各種變化的數據處理要求。具有高結構化設計,容錯及程序保護等設計。由于其獨到的性能,在航天領域得到了青睞。由于采用SOC方式,內部集成度高,外部擴展工作少,此本身具有較強的抗干擾能力;同時通過外部硬件電路以及軟件的抗干擾設計,平臺計算機可以實現非常高的可靠性。

RS422

3個UART控制器在SOC 中實現,通過RS422收發芯片將LVTTL電平轉換為RS422電平,其中1路RS422帶接收/發送中斷。

UART1 具有16 byte的FIFO,可產生中斷,取數后,清中斷,并同時清空FIFO。UART2 具有1K byte的FIFO,數據發送時由獨立管理器管理,不占用CPU時間。UART3 具有16 byte的FIFO,可產生中斷。

采用RS422總線接口,最大傳輸距離:1000m。為了提高抗干擾能力和較高的EMI防護性能,采用了光電隔離方式,提高了節點的穩定性和安全性。

頻標和5ms中斷

頻標和5ms中斷功能在SOC中實現。頻標默認頻率1ms,兼容TTL電平,50%占空比。在SOC中可通過配置不同的值輸出不同頻率的頻標,其啟動和關閉均可由軟件操作相應寄存器來控制。

5ms定時器模塊用于產生周期性的中斷請求,默認周期為5ms,其啟動和關閉均可由軟件操作相應寄存器來控制。

1553B部分

1553B總線與S698 IP核集成在一起,在SOC中實現。傳輸速度為每秒1M比特,字的長度為20個比特,數據有效長度為16個比特,信息量最大長度為32個字,傳輸方式為半雙工方式,傳輸協議為命令/響應方式,故障容錯有典型的雙冗余方式,第二條總線處于熱備份狀態;可通過軟件配置實現3個不同的終端,有總線控制器(BC)、遠置終端(RT)和總線監聽器(BM);信息格式有BC到RT、RT到BC、RT到RT、廣播方式和系統控制方式;能掛31個遠置終端,傳輸媒介為屏蔽雙絞線,總線耦合方式采用直接耦合方式。平臺計算機實現了完整的1553B總線的通訊,其包括BC、RT、BM,其功能、通信以及操作方式同BU-6158X芯片基本一致。一片能實現1553B功能的專用芯片DDC61580價格不菲,而且全面依賴進口。全面依賴進口的產品用在特殊領域也不適合,而我們在一款性價比很高的FPGA里就實現了實現DDC61580同樣的功能。

1553B總線控制器的主機接口有兩種:APB和AHB。主機(即SPARC V8處理器)通過APB接口(包括輸入總線APBI和輸出總線APBO)訪問寄存器,通過AHB接口(包括輸入總線AHBI和輸出總線AHBO)訪問存儲器。Manchester CODEC 的輸出/輸入為互補曼徹斯特碼,碼速率為1Mbps。信號RXA、RXAN、TXA、TXAN、TXAEN、RXB、RXBN、TXB、TXBN和TXBEN為1553B總線控制器同外置收發器芯片的接口信號。

本計算機平臺可以通過對1553B控制器寄存器進行配置,可以分別實現BC、RT、BM的功能。可以靈活應用在不同的場合。

VME部分

VME總線是一種應用較為普遍的計算機接口總線,技術成熟。目前國內外很大一部分的星載計算機并行總線都采用VME總線結構。VME總線是一種高速、異步并行數據傳輸總線,可在非多路、32位數據和地址通路上支持八位、十六位和三十二位的傳輸,通訊協議是異步和全掛鉤方式的。它包括的功能模塊有:主模塊、從模塊、中斷模塊和中斷管理模塊,另外還有兩個模塊:總線定時模塊和IACK菊花鏈驅動模塊輔助上述各個功能模塊。

本平臺計算機VME總線控制器在SOC中實現標準VME總線,VME總線信號從SOC出來后,經總線驅動電路,輸出到背板連接器。總線芯片采用74ALVC164245,實現3.3V ~ 5V電平轉換。VME接口與底板連接器有96個引腳,排列成三排,每排32引腳。VME控制器掛接在處理器外部存儲控制器總線上,映射的區域為I/O區,為其分配的地址區域為:0x24000000~0x24FFFFFF,共16M空間。

D/A轉換模塊

D/A轉換模塊由以下三部分組成:D/A轉換芯片、基準、運放。12位D/A轉換精度,可輸出4路+10V~-10V電壓

軟件編程

S698 IP核可以支持ucLinux,RTEMS,Vxworks等多種操作系統;也可不使用操作系統,支持標準C編程。而且開發了Linux和Windows下圖形化集成開發環境,支持流行的調試方法;開發環境支持離線仿真調試和目標板在線調試。

結語

這種高可靠平臺計算機,不再采用體積大、笨重而又功耗巨大的處理器芯片(如DSP),而是直接將S698 IP核放進FPGA。同時在硬件、軟件以及制板布線等方面采用多種提高系統可靠性的設計措施。系統將大部分的處理功能硬件化,利用FPAG的豐富資源,將整個系統放入一片FPGA芯片內。其中的S698 IP核進行控制管理和一些必須的計算處理。這樣的一款國產的高性能的處理器,具有自主的知識產權,應用在一些特殊的領域,對于國家安全來說尤為重要。S698 IP核在性能上也絕不遜色于其他同類處理器,豐富的外設,為用戶搭建了一個芯片級的高可靠計算機平臺,使用起來極為方便。

參考文獻:

1. 金永德等,導彈與航天技術概論,哈爾濱工業大學出版社,2002

2. 華容茂,數字電子技術及邏輯設計,中國電力出版社,2003

3. 美國國家標準-通用背板總線:VME總線IEEE標準

4. MIL-HDBK-1553A(美國軍方1553標準)

5. 周明光、馬海潮,計算機測試系統原理與應用,電子工業出版社,2005

6. 沈頌華,航空航天器供電系統,電子工業出版社,2005

7. 1553 User’s Guide. DDC公司,2003

8. MIL-STD-1553 DESIGNED’S guide,DDC公司, 2003

9. OBT-1553B User’s Guide,歐比特公司,2004

10. 平臺計算機User’s Guide,歐比特公司,2004

評論