基于CPLD的CMOS APS驅動時序的設計

1 引言

本文引用地址:http://www.j9360.com/article/86357.htmCMOS圖像傳感器是近年來發展十分迅速的一種新型固態圖像傳感器。它將圖像傳感器陣列、時序控制電路、信號處理電路、A/D轉換電路以及接口電路等集成在一體,使其具有體積小、功耗低、集成度高、控制簡單、成本低等優點,因此在數字圖像采集等方面得到廣泛應用。

本文在分析了PB-1024 CMOS APS圖像傳感器的工作原理和時序要求的基礎上,設計了簡單合理的時序控制電路。該設計采用復雜可編程邏輯器件(CPLD)作為硬件設計平臺,VHDL語言為設計描述方式,并通過Xilinx公司的Foundation軟件進行了系統仿真。

2 PB-1024 CMOS APS圖像傳感器

2.1 特性、結構及原理

PB-10244是美國Photobit公司生產的百萬像素CMOS APS圖像傳感器。其圖像分辨率為1024H×1024V,像元尺寸10.0μm×10.0 μm,在主時鐘頻率為66 MHz時,最大數據傳輸速率為528 Mbit/s,對應的采樣速率為500幀/s,且片內集成了8位A/D轉換器。

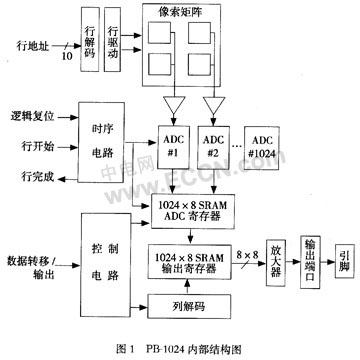

PB-1024 CMOS APS圖像傳感器將像素矩陣、A/D轉換電路及時序控制電路等集成在一起,其內部結構由圖1所示的幾個功能模塊組成。當光照射到像素陣列上時發生光電效應,在像素單元內產生相應的電荷。在時序電路的控制下,行選擇邏輯單元根據行地址總線選通相應的行像素單元,行像素單元內的圖像信號通過各自所在的列信號總線,傳輸到對應的模擬信號處理單元和A/D轉換器,轉換后的數字信號首先被存儲在A/D轉換寄存器中,然后在輸出控制電路的作用下,轉移到輸出寄存器中,最后8×8位的數字信號經放大后輸出。

2.2 時序分析

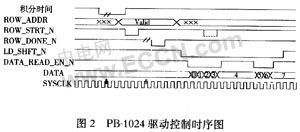

PB-1024 CMOS APS圖像傳感器所需的時序驅動控制信號主要有:采樣開始信號ROW_STRT_N、數據轉移信號LD_SHFT_N、數據允許輸出信號DATA_READ_EN_N等,其驅動控制時序如圖2所示。

在光積分期間,通過10位行地址總線(ROW_ADDR)選通有效的像素行,當采樣開始信號有效時(ROW_STRT_N為低電平),開始從有效的像素行中讀取模擬信號,經A/D轉換后,將數字信號存儲在A/D轉換寄存器中。完成以后,圖像傳感器送出數據讀取完成信號(ROW_DONE_N為低電平)給驅動控制器,驅動控制器發出數據轉移信號(LD_SHFT_N為低電平),此時數字信號從A/D轉換寄存器中轉移到輸出寄存器中。在數據轉移信號有效的一個時鐘周期后,數據允許輸出信號開始有效(DATA_READ_EN_N為低電平),數據從輸出寄存器中輸出。

3 時序控制電路的CPLD實現

3.1 復雜可編程邏輯器件

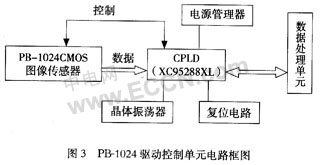

在設計中,由于來自PB-1024圖像傳感的8×8位數據輸出端口要用到64個I/O口、行地址需要10個I/O口、其他控制信號需要45個I/O口,這樣共需要119個用戶自定義的I/O口。為此選用美國Xilinx公司生產的XC95288XL復雜可編程邏輯器件來實現對PB-1024 CMOS APS圖像傳感器的驅動控制。XC95288XL共有208個輸出端口,其中有168個用戶可編程的I/O口,完全可以滿足系統設計的需求。基于CPLD的PB-1024 CMOS APS圖像傳感的驅動控制單元如圖3所示。

3.2 驅動電路的VHDL設計

通過對PB-1024 CMOS APS圖像傳感器的時序分析可見,時序控制電路的設計規模較大、復雜程度較高且速度要求較快,因此為了滿足高頻幀的時鐘要求,設計采用VHDL語言來實現,主要產生PB-1024的輸入時鐘信號和數據的采集、轉移和輸出信號。

為保證采集到的圖像能夠實時地顯示在XGA監視器上,系統時鐘頻率按照XGA監視器的掃描頻率75 Hz來確定。由于場消隱期的存在,即每一行的輸出信號都會包含一些啞像元,每一場圖像的輸出也會包含一些啞行,所以在設計時為保證不會采集到消隱電平,使每一個有效像素與每一位有效數據的輸出——對應,因此確定一場圖像的實際大小為1328×803。這樣得到的行頻為60.225 kHz,點頻為80 MHz,因此用80 MHz的時鐘頻率作為CPLD內部的全局時鐘頻率。但由于圖像在傳輸過程中受到低速XGA電纜發送速率75幀/s的限制,所以PB-1024 CMOS APS圖像傳感的輸入時鐘頻率只能達到10 MHz,這可由一個8分頻的計數器完成。

數據的采集、轉移和輸出的過程為:當全局復位信號RESET=1時,系統停止工作,這時所有計數器清零。當RESET=0時,系統處于采集狀態。采集一場圖像的過程為:當全局時鐘信號VCLK的下降沿來到時,列計數器(HCOUNTB)開始計數,在輸出若干個過渡像元后開始有效數據的采集和轉移(LD_SHIFT為低電平),在一個全局時鐘周期后數據開始允許輸出(DATA_READ_EN為低電平),當列計數器計數到1024時,停止數據的轉移和輸出。當列計數器計數到1327時,行計數器(RSTV-COUNT)加1,列計數器清零,開始下一有效像素行數據的采集、轉移和輸出。當行計數器計數到768時,完成一幀圖像的采集,當行計數器計數到803時,完成一場圖像的采集。

3.3 設計驗證

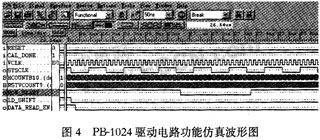

采用Xilinx公司的Foundation軟件對時序電路進行仿真,仿真波形如圖4所示。通過與圖2的比較,可以看出產生的驅動控制信號波形與PB-1024 CMOS APS圖像傳感器所需時序控制關系基本吻合,能夠達到PB-1024 CMOS APS圖像傳感器的時序要求。

4 結 論

采用CPLD對CMOS APS圖像傳感器的驅動電路進行設計,使原來復雜的電路設計變成只需一片CPLD芯片就能完成,而且電路成倍簡化、體積減小、功耗降低,從而提高了圖像傳感器的抗干擾能力、可靠性和穩定性。

評論