處理器核改進 引發能耗地震

根據摩爾定律,每18個月(起初是24個月)芯片上的晶體管密度就會翻番,但是前幾年功耗問題曾一度困擾Intel等公司的發展。為此,Intel對摩爾定律進行了大膽的修正,指出摩爾定律是晶體管密度、性能和功耗的折中發展規律。為此,多核開創了一個嶄新的計算時代。

本文引用地址:http://www.j9360.com/article/82667.htm

圖1 原摩爾定律不再有助于功耗降低

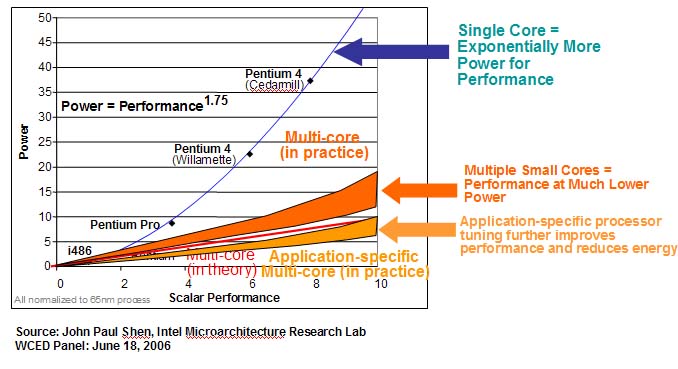

通常認為,多核設計與優化的處理器相互協同作用,才能帶來芯片能耗降低的地震(圖2)。多年來一直倡導在SoC中進行多核設計,在可配置多核方面獨樹一幟的Tensilica,在多核低功耗方面取得了巨大的突破,產品已經應用于Cisco ASR 1000F系列產品上,Cisco的QuantumFlow處理器采用了40核方案,Epson公司的PM-D870打印機采用了6核設計。

圖2 特殊應用處理器對改進性能和降低功耗幫助最大

在近日舊金山舉行了Electronic Summit2008上,Tensilica公司的總裁兼CEO Chris Rowen博士稱該公司處理器核功耗是其競爭對手的1/3,并介紹了開發秘籍:

1, 優化指令。Tensilica每個優化指令效率相當于普通的5~50個RISC指令;

2, 處理器核數量增加,但每個核幾何尺寸更小,每個小核完成專門的功能,例如有的做無線通信、有的管協議,有的處理視頻,有的音頻……;在整體設計時,如果需要控制功能,控制核可以是Tensilca的,也可以是ARM或MIPS等公司的。

3, 處理器核接口方面,為了方便實現多核,需要新的通訊支持,Tensilca的Xtensa處理器核有更多的指定內存(memory-mapped)I/O和直接連接選擇。

4, 建模和模擬工具Xenergy Energy Explorer在結構上進行了突破,包括建模和分析,軟件開發和調試等。

晶體管相關文章:晶體管工作原理

晶體管相關文章:晶體管原理

評論