基于Multisim的數字鐘實驗電路的設計與仿真

在電子技術實驗教學中,構建學生的電路設計理念,提高學生的電路設計能力,是教學的根本目的和核心內容。數字鐘電路的設計和仿真,涉及模擬電子技術、數字電子技術等多方面知識,能夠體現實驗者的理論功底和設計水平,是電子設計和仿真教學的典型案例。文中采用了555 定時器電路、計數電路、譯碼電路、顯示電路和時鐘校正電路,來實現該電路。

本文引用地址:http://www.j9360.com/article/270615.htm1 系統設計方案

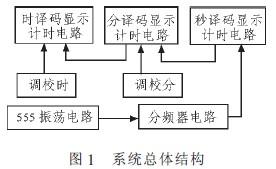

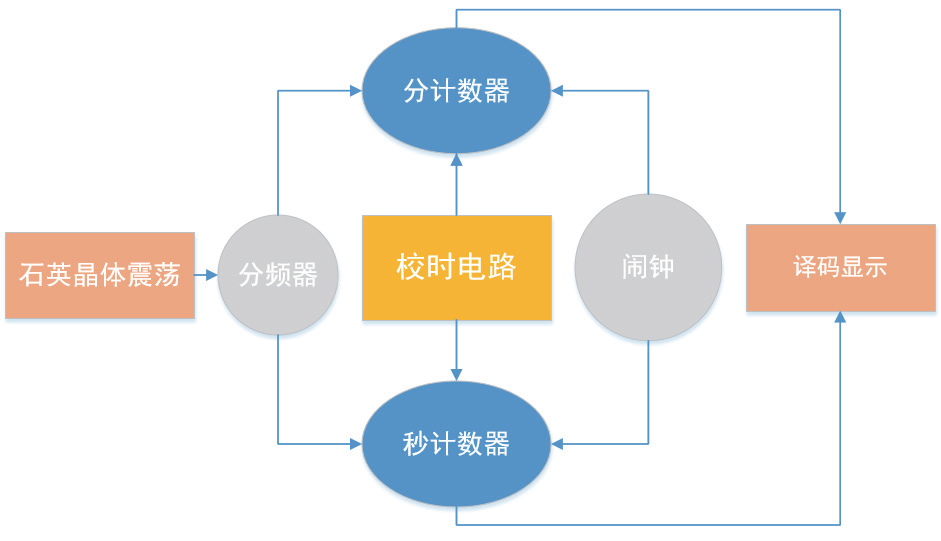

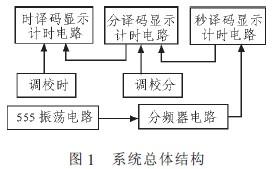

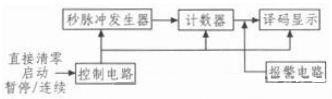

數字鐘由振蕩器、分頻器、計時電路、譯碼顯示電路等組成[1-3]。振蕩器是數字鐘的核心,提供一定頻率的方波信號;分頻器的作用是進行頻率變換,產生頻率為1 Hz 的秒信號,作為是整個系統的時基信號; 計時電路是將時基信號進行計數;譯碼顯示電路的作用是顯示時、分、秒時間;校正電路用來對時、分進行校對調整。其總體結構圖,如圖1 所示。

2 子系統的實現

2.1 振蕩器

本系統的振蕩器采用由555 定時器與RC 組成的多諧振蕩器來實現, 如圖2 所示即為產生1 kHz 時鐘信號的電路圖。此多諧振蕩器雖然產生的脈沖誤差較大,但設計方案快捷、易于實現、受電源電壓和溫度變化的影響很小[4]。

2.2 分頻器

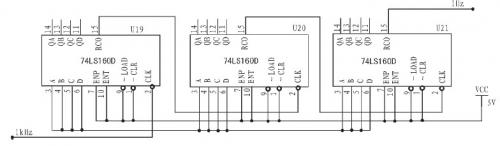

由于振蕩器產生的頻率高, 要得到標準的秒信號,就需要對所得到的信號進行分頻。在此電路中,分頻器的功能主要有兩個:1) 產生標準脈沖信號;2) 提供電路工作需要的信號,比如擴展電路需要的信號。通常實現分頻器的電路是計數器電路,選擇74LS160 十進制計數器來完成上述功能[5]。如圖3 所示,555 定時器產生1 kHz 的信號,經過3 次1/10 分頻后得到1 Hz 的脈沖信號, 為秒個位提供標準秒脈沖信號。

2.3 時間計數器

計數器是一種計算輸入脈沖的時序邏輯網絡,被計數的輸入信號就是時序網絡的時鐘脈沖,它不僅可以計數而且還可以用來完成其它特定的邏輯功能,如測量、定時控制、數字運算等等。

本部分的設計仍采用74LS160 作為時間計數器來實現時間計數單元的計數功能。時間計數器由秒個位和秒十位計數器、分個位和分十位計數器、時個位和時十位計數器構成。數字鐘的計數電路的設計可以用反饋清零法,當計數器正常計數時反饋門不起作用,只有當進位脈沖到來時,反饋信號將計數電路清零,實現相應模的循環計數。

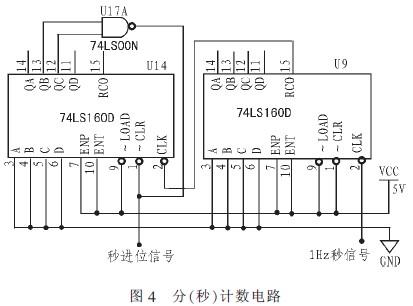

2.3.1 分(秒)計數器

分(秒)計數器均為60 進制計數,如圖4 所示。它們的個位用十進制計數器74LS160 構成,無需進制轉換,信號輸入端CLK 與1 Hz 秒信號相連,進位輸出作為十位的計數輸入信號。十位采用反饋清零法將十進制計數器74LS160 變成六進制計數器,因為清零端為低電平有效、所以將QB、QC與非后連接到清零端, 即計數器的輸出狀態為“0110”時QB、QC 輸出高電平與非后為低電平實現有效清零并對下一級進位。兩級電路組成一位60 進制計數器,其計數規律為00→01→…→58→59→00。當秒計數滿60 后向分個位提供一個進位信號,同理當分計數滿60 后向時個位提供一個進位信號。

模擬信號相關文章:什么是模擬信號

分頻器相關文章:分頻器原理 脈沖點火器相關文章:脈沖點火器原理

評論