富士通Custom SoC:大數據背后的高性能設計的功耗挑戰

歲末年初,當我們回顧2014年產業界的發展時,少不了IoT(物聯網)和Big Data(大數據)這兩個2014年科技界人們談論最多,捧的最高的科技名詞。在IEEE公布的2014 TOP10熱搜排行榜上,他們也榜上有名。不過,撥開他們華麗的外衣,我們看到的是隱于其背后的各種先進的高性能及超低功耗半導體技術令人驚喜的發展。

本文引用地址:http://www.j9360.com/article/267367.htm功耗成為HPC和Networking的關鍵設計挑戰

毫無疑問,IoT促進了低功耗的發展,但是,這只是問題的一個方面。另一方面,無所不在的移動設備產生了巨大的數據洪流,越來越多的遠程監控系統以及嵌入式系統也產生了龐大的數據集,一些數據流只是在網絡上流過而已。而有些會進行精細的分析,例如,從監控圖像流中找出綁架了兒童的汽車牌照,或者每月才出現一次的希格斯玻色子等。大數據迫使我們大幅度提高網絡和計算帶寬。不過,在為數據中心加速的同時,功耗的問題就擺在眼前。

“大多數人們對于能耗受限的深切認識到來源于移動設備的電源續航能力的限制,這就給我們造成了一種錯覺,以為只有移動設備是功耗敏感的應用,其實,在諸如數據中心等的高性能計算(HPC)及網絡(Networking)領域,對于功耗的要求更加的苛刻。”富士通半導體市場部經理陳博宇(Alex Chen)先生在一年一度的中國集成電路設計業年會暨中國內地與香港集成電路產業協作發展高峰論壇(簡稱ICCAD峰會)上表示。

?

富士通半導體市場部經理陳博宇 在ICCAD上演講

和手機固定功率的電源不同,數據中心的電源是永遠開啟的,整個機房的每個芯片無時無刻不在工作,對整個供電系統,包括散熱系統的壓力巨大。據統計:當服務器小于1萬臺,全年耗電約0.35億千瓦時(電是次要因素);當服務器小于10萬臺,全年耗電約3.5億千瓦時(電是重要因素);當服務器小于50萬臺,全年耗電約17.5億千瓦時(電是主要成本);當服務器小于100萬臺,全年耗電約35億千瓦時(電是TOP1成本)。

而和消費類的應用非常不同,在通信領域,對每個板卡的功耗都有要求,只有達到每塊板卡的功耗要求,整個系統的功耗才能達標。“在高性能應用領域,億門級的設計規模使得芯片的復雜度增加,如何在功耗上進行優化,而又能達到性能要求,這是在大規模設計上特別要考慮的。” 陳博宇指出。

多種方法應對高性能設計的功耗挑戰

現在的高速低功耗設計,最多有超過7億多門級電路和超過2GHz的工作頻率的設計。因此,設計人員需謹慎評估如何在最短的設計周期內,針對整個芯片的低功耗策略做定義及最佳化,并思考如何讓封裝設計滿足超高的功耗。

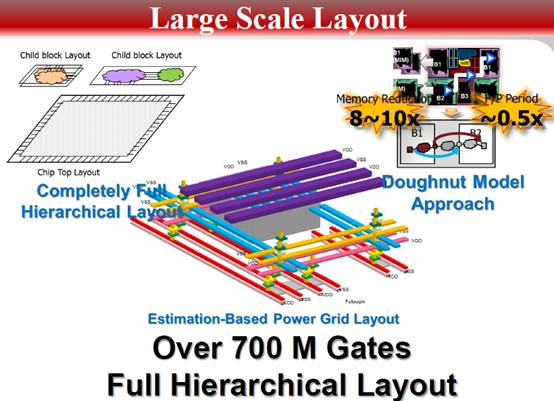

大規模版圖設計能夠幫助設計人員應對高速低功耗設計挑戰,如下圖所示2,富士通半導體的協同設計技術優化了芯片、IP、及從封裝到板級設計等所有方面。為使其達到性能最優化,貫穿規劃,設計,建模和分析所有過程,富士通半導體使用了可以預估的電源網絡構架,并使用了層次化的電源網絡分析,這種分析可以優化電源網絡設計,并且最小化全芯片的功耗。低噪聲的芯片架構設計可以承受超過300瓦的功耗。

?

大規模版圖設計 幫助設計人員應對高速低功耗設計挑戰

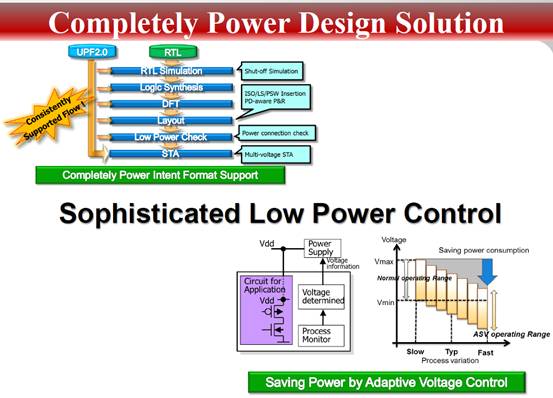

此外,特別值得一提的是富士通半導體獨特的ASV(Adapter Support Voltage)技術。如下圖3所示,該技術用以監控制程(process)的快慢。

?

全功耗設計解決方案應對高速低功耗設計挑戰

陳博宇進一步解釋:“因為晶圓廠的制程存在快(fast)、慢(slow)、標準(typ)的狀態,在芯片中放置’Process Monitor’,使得我們可以讀出制程的參數,這樣就能知道電源的大小,例如,如果我們讀出是偏快的制程,就可以幫助降低電壓,因為功率是和電壓的平方成正比,所以降低電壓就能降低功耗,ASV技術就像一個彈簧一樣,把芯片拉向typ。”

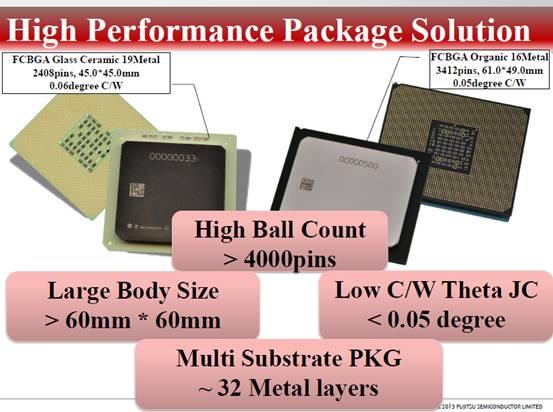

再次,高性能封裝解決方案在應對功耗挑戰上必不可少。富士通半導體在高性能封裝市場也處于領先地位,在開發這些高可靠性封裝的過程中,富士通半導體進行了嚴謹的模擬,優化了技術原型。如下圖4所示。

?

高性能封裝解決方案應對高速低功耗設計挑戰

“我們的球形封裝技術支持到超過4000個pin腳,并且每一邊的封裝尺寸可以到達60mm,我們的多層基板封裝設計可以支持到32層,對于BGA封裝,我們獨特的金屬TIM實現了超低Theta JC,Theta JC小于0.05度,并通過了最新的熱阻測量技術驗證。我們正在為中央處理器和服務器,研制新一代2.5和3D封裝技術。” 陳博宇表示。

評論