富士通Custom SoC:大數據背后的高性能設計的功耗挑戰

極具競爭的高速設計解決方案

本文引用地址:http://www.j9360.com/article/267367.htm隨著芯片的處理速度不斷提升,工作頻率甚至超過2GHz,在高速設計中往往需要整合數億顆同時運行的晶體管和超高速模擬互聯IP,導致物理設計收斂變得更為困難,而芯片上大量的數字電路對超高速模擬IP的干擾現象也日益明顯。

一方面,為實現高速設計富士通半導體使用了復雜的時鐘分布技術,實現了低時鐘偏差,并使用金屬層隔離實現了無噪聲設計,其先進的層次及緩沖器優化技術能夠控制金屬層的優化。

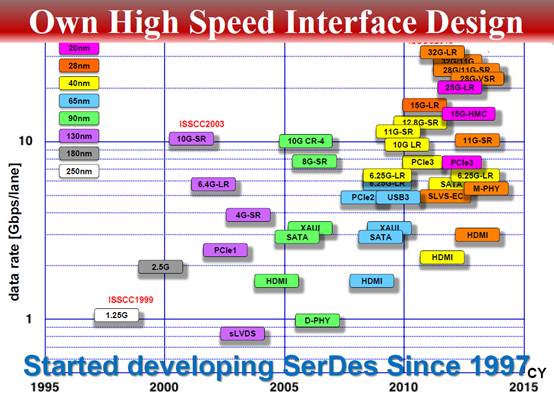

另一方面,自1999年富士通半導體研發出了超過1Gbps全球最快的SerDes以來,此后很多年,富士通半導體一直都是高速接口設計的領軍者,滿足了計算機網絡設計,伺服器和消費電子的需求。現在富士通半導體的SerDes支持速率達到了32Gbps,并支持客戶專用定制。針對最新32Gbps SerDes的評估板也以投入使用,未來還將支持56Gbps SerDes或更高參數。

如下圖5所示,富士通半導體廣泛的高速IP產品組合包括非常高速的SerDes,及PCIe和SATA等,這對于用戶具有非常獨特的價值,也是一般的IC設計服務公司所不具備的能力。“富士通半導體能夠提供給客戶整套的方案,我們寬泛的高速IP接口是經過驗證的,用戶采用我們的方案不會有IP驗證方面的后顧之憂。” 陳博宇表示。

?

高速接口IP積累

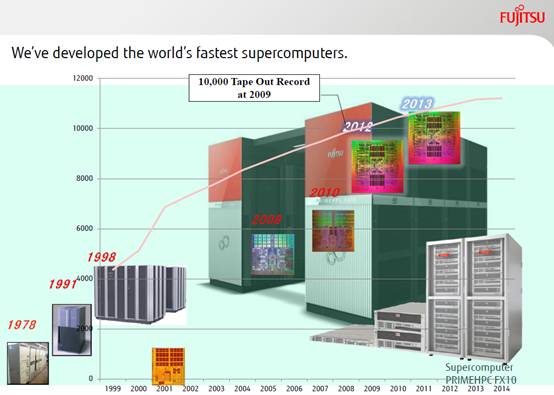

50年磨一劍,在Custom SoC (ASICs)積累豐富Know-how

現在,富士通半導體擁有大規模版圖經驗,高速接口,高性能封裝經驗和協同設計能力,從設計到交付,始終支持客戶的高性能LSI項目。

“從1956年出口了第一批硅晶體管開始,50年來,我們一直致力于對現有產品的不斷提升并持續開發新產品。在Custom SoC (ASICs)領域積累了豐富Know-how。并且在HPC和Networking設計中,有很多成功的案例。2009年,我們的Tape out總數達到10000個,每年的Tape out數量都增加300多個。” 陳博宇指出。

?

2012年,富士通研發的超級計算機

2012年,富士通半導體參與研發出了當時世界上最快的超級計算機“京”,“京”的計算速度為每秒1.051萬萬億(1萬萬億為1京)次。

據悉,富士通半導體與國內知名的網絡芯片提供商在最近的一次高頻通訊ASIC芯片的合作開發中,雙方共同克服效能、功耗和交期的挑戰,且原型芯片的Tape out比原定計劃提前兩周,并一次成功。陳博宇進一步表示:“我們現在做的比較多的是在2億到3億門規模左右的設計,以28nm為主,預計接下來兩年會有若干個16nm/14nm的2億、3億門級的設計。”

評論