基于ARM+FPGA的大屏幕顯示器控制系統設計

0 前言

本文引用地址:http://www.j9360.com/article/261853.htm隨著計算機和半導體技術的發展,LED大屏幕顯示系統成為集計算機控制、視頻、光電子、微電子、通信、數字圖像處理技術為一體的顯示設備。目前LED大屏幕顯示器向更高亮度、更高耐氣候性、更高的發光均勻性、更大屏幕化、更高的可靠性方向發展。LED顯示屏產業正成為我國電子信息產業的重要組成部分。大屏幕顯示技術的發展進步,需要處理的數據量大大增加,系統的頻率越來越高,系統的規模越來越大,對顯示控制系統的要求不斷提高。以往的LED大屏幕顯示系統用中小規模集成電路實現,系統體積較大、調試困難、不易修改。隨著半導體技術的進一步發展及大規模集成電路的廣泛應用,ARM具有體積小、功耗低、數據處理能力強等特性,PLD能夠滿足LED大屏幕系統高速圖像數據傳輸對速度的要求且設計靈活。鑒于此,本設計采用ARM+RAM+FPGA方案,解決了系統的運行速度、尋址能力和功耗等問題,從而支持更大可視區域的穩定顯示,存儲更多的顯示內容。

1 系統組成及原理

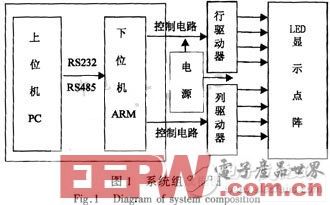

該系統主要由PC機、顯示控制電路和LED顯示屏3部分構成,如圖1所示。

PC機在控制中作為上位機,用于后級下位機ARM的控制和管理。上位計算機主要用于人機交互,完成對顯示控制電路的顯示數據發送以及設置LED顯示屏的顯示效果。用戶在上位機上通過控制軟件將編輯好的文字圖片信息和相應的控制命令通過串行通信傳輸至系統的控制電路部分,LED顯示屏即可根據用戶選擇的方式循環顯示用戶編輯好的文字和圖片,該系統還具有脫機顯示的功能,用戶將顯示的內容傳送至顯示控制電路部分后,上位計算機就可以不再介入顯示的過程,顯示系統可以根據用戶設定的模式顯示所要顯示的信息內容。數據轉換信號控制部分采用ARM實現,LED顯示屏的掃描驅動電路采用 FPGA來完成。上位機與下位機之間的通信采用標準的RS232/RS485計算機數據串行通信方式,它們相對獨立,但相互間協調工作。顯示屏以LED為像素,由LED點陣顯示單元拼接而成的,本設計的顯示屏為16行×256列,采用640×480點陣結構。

2 系統硬件設計

2.1顯示控制電路

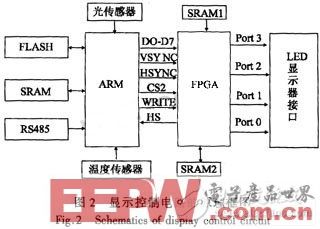

顯示控制電路系統的重要部分,主要由輸入接口電路、數據轉換及信號控制電路、掃描驅動電路組成,如圖2所示。

當顯示屏做得越大,即屏幕的點陣越多,向顯示屏發送的數據就越多,數據傳輸與控制的時間也會增加,完成一屏掃描的時間會越長。因此,在設計中必須考慮這個因素。滿足這一要求,關鍵在于提高程序的執行速度,可以選擇更快的CPU或數字信號處理芯片ARM。本設計采用基于ARM的32位嵌入式 RISC為處理器,S3C4510B是完全可以勝任的,該微處理器的速度較高,而且存儲容量較大。

上位機通過串口經過RS232/RS485轉換器將指令集發送給ARM微處理器,ARM微處理器把接收到的指令集放入外部的FLASH中保存,斷電后內容不丟失,同時ARM外部擴展兩片SRAM用于存放快速運算的數據,光傳感器和溫度傳感器用來測量外界的光和溫度,以便隨著光線的強弱改變顯示屏的亮度,在顯示屏上顯示出外界溫度。FPGA完成對LED屏的掃描驅動過程,其內部固化的數字邏輯負責產生屏幕顯示控制信號(串行移位時鐘、行鎖存信號、行選信號等),其外部配置的兩片SRAM用于分時讀取灰度數據。同時,FPGA從 SRAM中讀取灰度數據信號,并將其轉換成上屏數據后串行輸出到相應的顏色的信號數據總線上。FPGA外部擴展的兩片SRAM組成了數據緩沖、切換區,采用乒乓邏輯,某一時刻向一片存儲器寫入數據,另一片被FPGA邏輯讀取數據轉換后送人顯示屏,二者輪流切換,保證了數據的高速上屏和顯示的連續性。ARM外部配置大容量的SRAM和FLASH存儲器,與傳統的顯示屏控制電路相比較,可以支持更大的顯示區域、存儲更多的顯示內容、獲得更好的顯示效果。

2.2掃描驅動電路設計

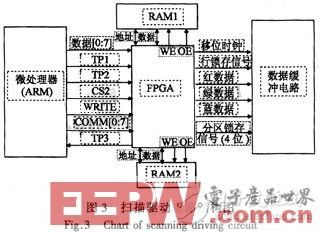

LED顯示屏的掃描驅動電路部分是由FPGA來實現的,如圖3所示。

掃描驅動電路主要完成灰度數據的讀取和發送、上屏灰度數據的產生、移位時鐘的產生、亮度信號的控制、4個分區鎖存信號的產生、通知ARM發送數據等功能。這些功能均在一片FPGA中完成,這樣使顯示控制電路板的體積減小,而且由于FPGA功能用硬件描述語言VHDL編程實現,即可以通過使用VHDL語言編程,來驗證系統方案的可行性及正確性,然后再用FPGA硬件來實現,從而可以大大縮短開發周期,使設計靈活、修改方便,同時FPGA由于高集成度、高速高可靠性、開發周期短的特點,從而大大改善電路性能。

這種設計的實現需要FPGA提供大量的I/O引腳,其中I/O引腳包括(1)系統總線接口:數據總線8根,控制信號線5根,亮度信號線3根,輸入線1根,復位信號線1根,共18根;(2)雙體SRAM總線接口:地址總線15根,數據總線8根,讀寫控制信號2根,共50根;(3)顯示控制信號輸出接口:移位時鐘信號1根,行鎖存信號1根,行選4根;(4)顯示像素數據輸出接口:紅、綠、藍共3根。共計18+50+6+3=77個I/O口。為了可以使LED顯示屏的尺寸增加1倍,即所需的I/O口增多,同時考用VHDL語言描述的內部功能邏輯所需的宏單元數量,需要選擇256個宏單芯片,在此 FPGA選用32位的PolarPro QLlP300芯片。

2.3靜態存儲器SRAM的選擇

外部擴展的兩片SRAM,要求能滿足上屏數據讀取速度的要求,考慮到存儲數據的寬度和容量,本設計選用ISSI(Integrated Silicon Solution Inc.)公司的IS61C1024芯片。該芯片存儲容量為128 kB,8位數據寬度,最高讀寫速度為25 ns,電源電壓為5 V,具有最高40 MHz的讀寫頻率,可進行高速異步讀寫操作,無須等待時間,其容量滿足一屏文字和圖像數據信息的存儲要求,兩片SRAM采用雙體切換技術來完成數據的存儲和讀取過程。

fpga相關文章:fpga是什么

led顯示器相關文章:led顯示器原理

三相異步電動機相關文章:三相異步電動機原理

評論