微帶濾波器和耦合電路的設計

1 前 言

當今的微波設計師依靠很多工具來制作高效的電路和系統。他們要利用已有的參考資料和強大的EDA工具和電磁(EM)分析工具,還必須結合自己的實踐經驗來 進行制作。這些工作終極需要通過制作電路和測試完成的電路來實現。這篇文章描述了兩個微帶電路設計是如何使用各種不同工具開發,用電路板銑制設備快速制 作,然后經過丈量來驗證設計方法的正確性。

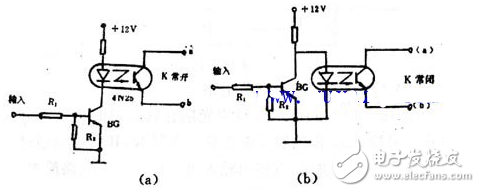

樣例中的設計是一個典型的帶寬3.7到4.2GHz的發夾型濾波器和一個1到8GHz的定向耦合器,使用Schiffman鋸齒技術減小尺寸。發夾型濾波器用Agilent ADS1.3軟件設計和仿真,用SONnet Lite軟件進行平面EM分析。耦合器運用了基于設計規則的變換,有一個現存的門路線形式的耦合器設計來啟動。

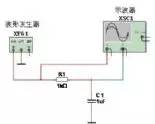

兩個電路都是用LPKF光電股份有限公司的Protomat C100HF型設備制作出來的,使用HP(Agilent) 8753E網絡分析儀獲得丈量結果。

2 設計樣例

3.7到4.2GHz的發夾型濾波器

2.1 設計

這個濾波器設計用于在3.7到4.2GHz的帶寬上獲得一個平坦的響應。插進損耗和回波損耗在此頻段優于16dB。這個濾波器用在下變頻器輸進端進行鏡頻抑制。該設計選用一個典型的發夾型濾波器,它將能滿足設計要求的性能和尺寸。

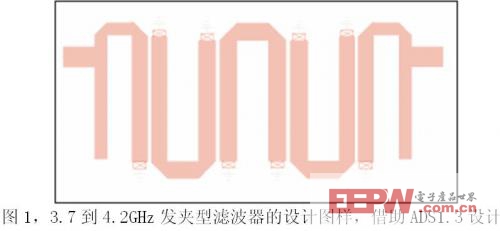

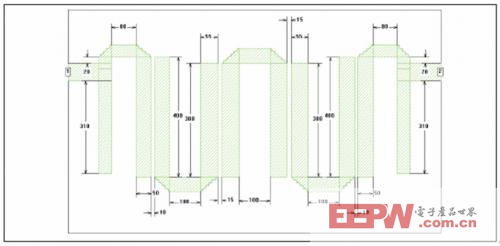

濾波器由ADS1.3設計,圖1是結果圖樣。當然,這是一個熟悉的發夾型結構。濾波器占用的面積約為500 x 1200 mils (0.5 x 1.2 in.),包括用來保持恒定邏輯屬性的發夾循環所需的足夠面積。

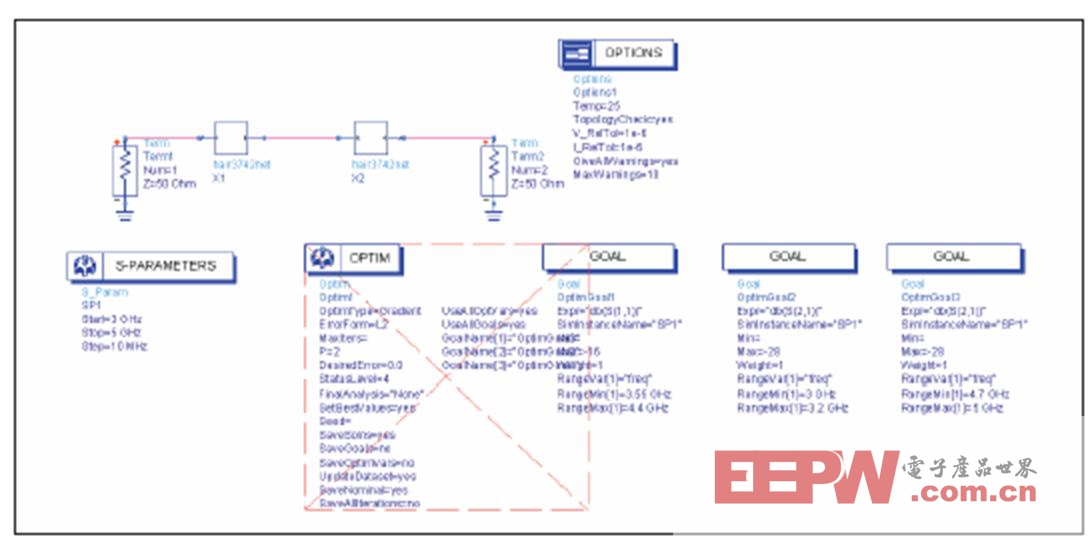

圖2是在ADS中的設計和優化結構。這個拓撲形是中心對稱的,所以設計成兩段,由一個“背靠背”結構連接。由于數學方面上的結構尺寸減小,計算時間被大大縮減。

圖2,在ADS中的設計和優化結構。濾波器以兩個鏡像的圖形塊進行仿真,以實現對稱結構

建立優化來獲得在通帶3.55至4.4GHz的最小16dB的回波損耗,在3.2GHz以下和4.7GHz以上最小28dB的阻帶衰減。優化的頻率范圍是3.0-5.0GHz。更寬范圍不要求獲得預想的結果。

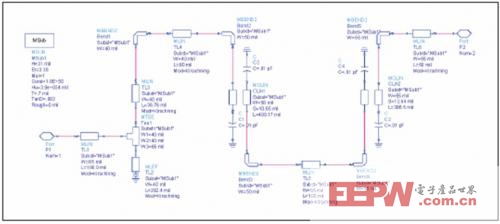

圖3,對終極設計的ADS仿真定義。仿真性能和濾波器圖樣都出自于這里的數據

圖3顯示了每一個“半濾波器”的ADS終極設計,包括端口、微帶線、T形、彎曲和短凸形。留意短凸形的末真個0.1pF電容,說明具有末端效應(邊沿電容)。圖1的也有它們的顯示。

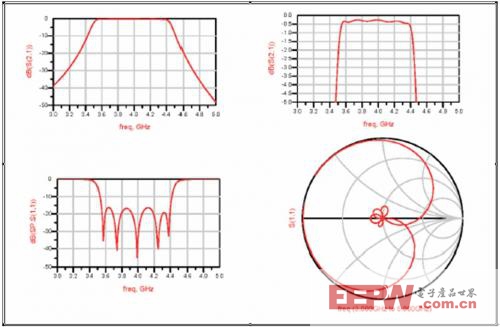

圖4,仿真結果。

(a)全程響應;(b)通帶響應和插進損耗;(c)回波損耗;(d)Smith阻抗圖

圖4是模型化的性能顯示。包括通帶、阻帶特性、回波損耗結果以及輸進/輸出阻抗的Smith圖。這些圖表說明ADS模型滿足濾波器的設計標準。

2.2 EM分析

圖5是濾波器尺寸的詳圖。設計的數據使用Sonnet軟件公司的Sonnet Lite平面電磁場軟件進行電路分析。

圖5,濾波器的具體尺寸。

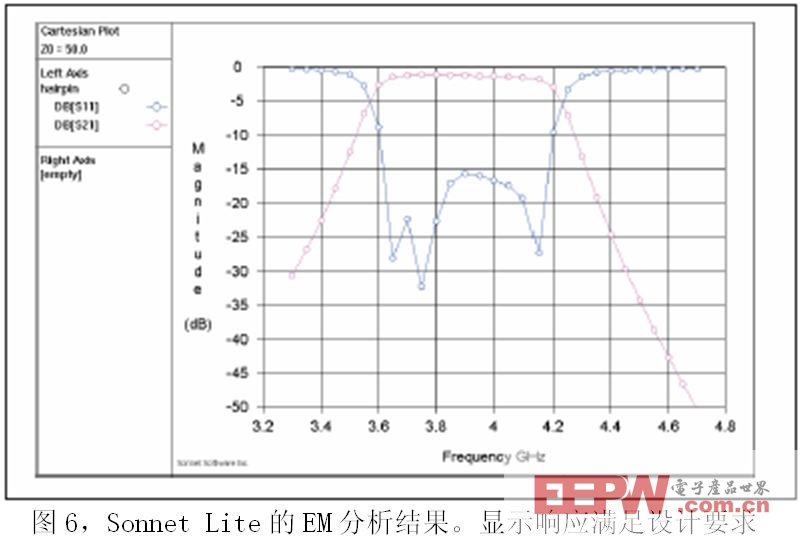

圖6是EM分析結果。通帶的響應比ADS預期的稍稍窄一些,但是假如制作出來的電路性能滿足分析的話,仍將覆蓋3.7到4.2GHz的帶寬。通帶的平坦性 非常接近ADS模型。回波損耗的響應在通帶上比ADS仿真的對稱性稍差一些。但仍能保持16dB或更好。

評論