微帶濾波器與耦合器電路的設計,制作與測量

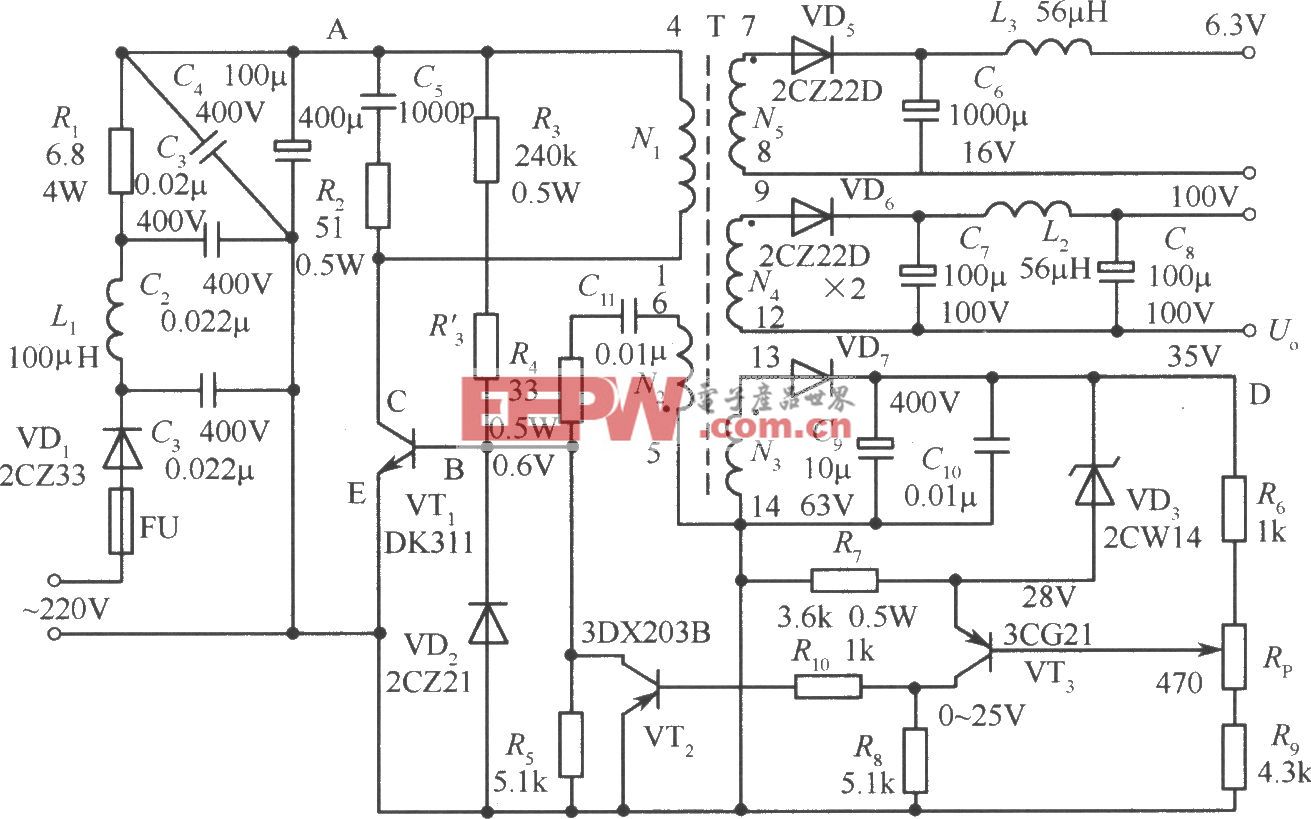

今日的微波設計者使用多種工具以幫助自己實現有效的電路和系統設計。他們借助的資源包括他們的參考書庫,功能強大的EDA軟件,電磁(EM)分析工具,以及 他們的個人經驗。通常,他們的設計需要通過制作最終的電路板成品,并對其進行測試來得到驗證。我們用不同的設計方法設計了兩種微帶電路,并且利用電路板雕 刻機快速制作了樣品;根據兩個樣品的測試結果的比較來判斷這兩種設計方法的優劣。

本文引用地址:http://www.j9360.com/article/259749.htm

要求設計的樣品是經典的發夾式濾波器,帶寬要求在3.7 到4.2GHz;還有一個1到8GHz單向耦合器,我們使用了Schiffman鋸齒技術來減小它的尺寸。發夾式濾波器使用Agilent公司的 ADS1.3[1]來做設計和模擬,而平面電磁分析則利用Sonnet Lite [2]完成。與此不同,耦合器的設計從已有的階梯線耦合器開始,采用了設計規則變換的方法來完成。以上的兩個電路都使用了LPKF激光電子的 ProtoMat C100HF電路板雕刻機完成制作。結果使用HP (Agilent) 8753E網絡分析儀做了測量。

設計實例 #1:一個3.7GHz到4.2GHz的發夾式濾波器

這個濾波器要求在3.7GHz到4.2GHz波段內平直響應,并且插損和回損要求控制在16dB以內。我們選擇了經典的發夾式設計,因為經驗告訴我們,它能夠達到所要求的性能和尺寸。

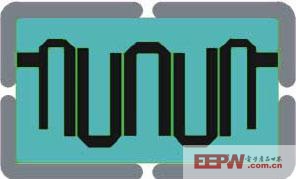

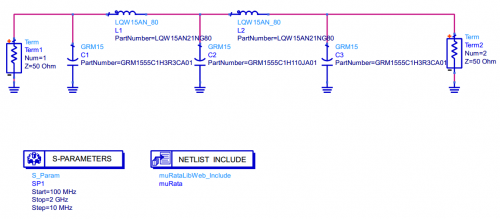

這個濾波器使用ADS1.3設計,設計圖見圖1。這個當然就是我們所熟悉的發夾式設計。濾波器所占據的面積大約是0.5*1.2 英寸,另外還要加上發夾電路外足夠大的面積來保持介電特性的一致性。

圖2是ADS中的設計和優化設置。由于這個拓撲結構是中心對稱,它被設計成兩部分背靠背的形式。如此一來,對稱的設計讓之后的模擬計算變的簡單,計算的時間大幅減小。

優化所設定的目標是以最少16dB的回損實現3.55到4.4GHz范圍內的帶通濾波,3.2GHz以下,4.7GHz以上28dB stopband attenuation。優化的頻率區間是3.0到5.0GHz。更大的范圍沒有必要。

圖3是ADS給出的每個濾波器的最終設計圖,包括了端口,微帶線,T字,轉角以及stubs。注意到stub末端的0.1pF的電容end effect(散射電容)。這些在圖1中也有。

該模型的性能由圖4給出。這些圖顯示了ADS模擬的帶通,截止,回損的結果以及輸入輸出阻抗比的Smith圖。這些圖顯示,ADS的設計模型能夠滿足濾波器相應的設計標準。

EM分析

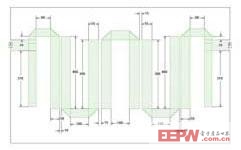

圖5是表示濾波器的所有尺寸。這份設計圖被Sonnet Lite平面電磁場分析軟件用來做電路性能分析。

圖6是EM分析的結果。這里的帶通波段比ADS預言的略窄,但是已經包含了3.7到4.2GHz波段。通帶平整度與ADS給出的結果非常接近。通帶內的回損響應沒有ADS給出那么對稱,但是在整個范圍內保持在16dB 左右。

圖6 Sonnet Lite的EM分析結果。從結果可以看出相關響應滿足設計標準。

制作測試濾波器

為了比較發夾濾波器的設計模型和實際效果,我們在微波覆銅板上使用雕刻機制作了一個測試樣品。

ADS的設計圖樣,經過簡單處理之后,變成雕刻機的驅動文件。設計圖中的相應尺寸被直接調用到LPKF的配套軟件中。圖7是LPKF CircuitCAM產生的加工數據。

性能測試

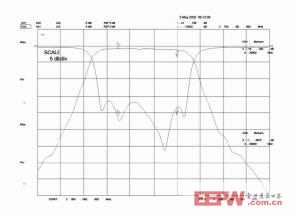

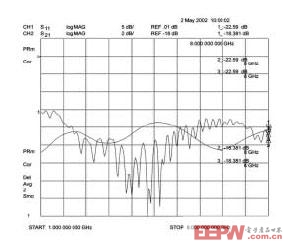

板子被銑成設計圖樣后,我們兩端接上連接器,并且用HP 8753E網絡分析儀對濾波器進行了測量。圖8是樣品濾波器的透過性能 (S21) 以及回損 (S11)測量值。這個圖的比例是每格5dB,用以說明整體通帶/截止性能小于-45dB。

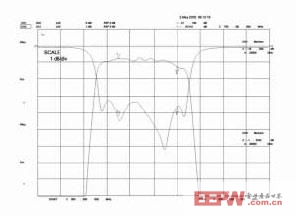

圖9與圖8相同,不過帶通的比例為每格1dB,用以說明通帶的平整度。圖中回損依然是每格5dB。

實測結果與模擬結果符合的很好。通帶比ADS預言的稍窄,但比Sonnet Lite給的值小。三種建模方法和測量結果在插入損耗和通帶平整度方面都符合得很好。

盡管從回損的形狀上講,模型和實測結果都各不相同,但是每一個都達到了16dB的規格要求,而且清晰顯示出多極濾波器特有的駝峰響應。

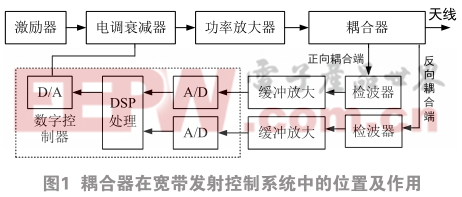

設計實例 #2:一個縮小了的階梯線單向耦合器

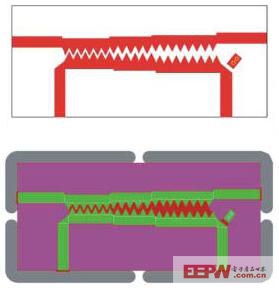

下一個我們將要檢查的電路是用經驗技術開發的。我們想要考察一種減小微帶電路尺寸的Schiffman方法, Uysal[4]在他的文章中詳細論述了這種方法。這一技術使用鋸齒或之字結構來減少給定電路的機械長度。

一 個由CAP Wireless職員Paul Daughen-baugh使用ADS設計的1到8GHz階梯線耦合器被作為設計底稿。設計的最終結果被導出到CircuitCAM軟件,經過簡單處理之 后,輸出成雕刻機能夠識別的設計圖樣,見圖10。這張圖清晰展示了這一技術。

我們采用了一種經驗的方法來從直條的耦合器得到鋸齒狀的耦合器,具體規則如下:

- 閉合空間耦合器部分——要求之字線的總長與這部分的直線長度相等。這就使得這個部分的尺寸縮小了將近一半。直線之間的間距保持不變。

- 開放空間耦合器部分——這個第三部分的線間距由鋸齒的中心高度為準計算的。在這個開放空間,我們假設場將根據這個平均空間來耦合,而不是沿著第一部分的邊緣線。同時,在這一部分長度的將小將相對較少。作為簡化,我們采用了與最初直線部分相同的長度。

- 中心部分——中心部分線間距和長度較小是根據第一和第三部分的幾何平均值計算而得的。

這個“最佳猜想”方法是必要的,因為不可能使用現有的軟件對這個結構進行分析。甚至對Sonnet Lite而言,都已經過于復雜。

耦合器性能

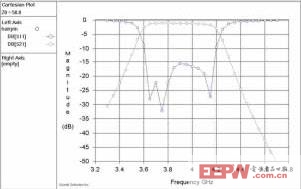

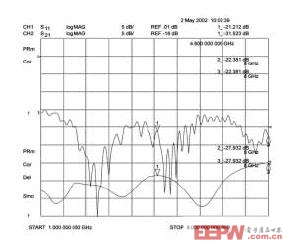

耦合器利用LPKF雕刻機制作完成后,我們在1到8GHz間對耦合度進行了評估。在圖11中,耦合端口傳輸是那條相對平滑的線。圖中的中心水平線為 -18dB,每格表示2dB。在整個測量頻率范圍內,耦合值為–19 dB ±1.5 dB。在同一副圖中,輸入回損為每格5dB,從上往下數,第二條線表示0dB基準線。最壞情況的回損在最低頻率處,為16dB。

圖 12表示逆向耦合的情況,包括了輸出端口回損。兩個圖的分辨率都是每格5dB。對于逆向耦合,中心線依然是-18dB基準線,耦合值在整個波段中好于 -28dB,除了高頻端處處好于31dB。輸出端口回損的比例與圖11中的相同,同時也在1GHz時有最差的16dB響應。

除了超高頻區域,方向性(前向耦合減去逆向耦合)總體保持在10dB。設計目標是大于10dB,實際設定目標為12dB,以便保留足夠的富余。對大多數的波段,目標都已經達成,我們認為,對初次嘗試而言,這已經是非常不錯的結果了。

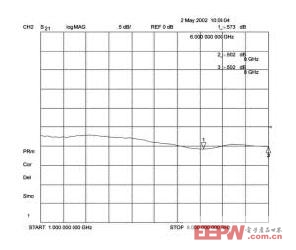

圖13是插入損耗,它在1GHz時,為0.25dB;在6GHz時,有一個0.57dB的最壞結果。從1到8GHz范圍內,插入損耗的變化不超過0.33dB。

樣品板銑制機的使用

快速制作樣品電路板能夠徹底改變某些設計的工程實現方法。以單向耦合器為例,我們一開始準備做多次反復的設計以獲得需要的性能。帶著幾分運氣(還有經驗基礎上的猜想),第一次嘗試就獲得了一個好的耦合器。

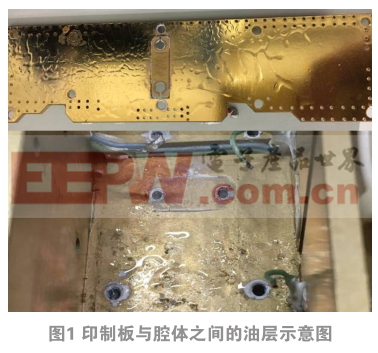

圖14和15展示了銑制得到的電路板,在上面已經安裝了連接器以供測量之用。圖14展示的發夾式濾波器電路甚至顯示出一小塊經過焊接的電路,這是為了填補微帶線路的一個缺口。這是由于設計圖樣上有一個很小的差錯,在板子完成時,才被發現。

耦合器設計可能還需要修改以便改進低端回損或者讓響應更平坦。這些細小的改動可能不會被使用傳統電路板制作方法的公司考慮。隨著環境規則的變化,特別在加州,額外的環境費用和復雜的工藝流程使得大多數的公司不再保留室內蝕刻實驗室。

總結

我們希望通過這些實例能夠清楚展示我們是如何使用諸多設計資源的。為了設計和制作這些濾波器和耦合器電路,幾個工程師的經驗再加上參考書,先進電路理論模擬,電磁分析還有制作和測量才能完成。過程中的每一步都會影響最終的設計的成敗。

濾波器相關文章:濾波器原理

濾波器相關文章:濾波器原理

電源濾波器相關文章:電源濾波器原理

評論