SoC存儲器的智能電源連接方法

簡介

SoC設計也面臨著一系列的難題和挑戰,其中出現的最大挑戰之一是硬核IP模塊集成和驗證。隨著技術的擴展,設計并集成IP模塊變得越來越難。在深亞微米技術設計中,IR壓降往往會對功能性造成顯著的影響。

本文介紹了一種新的IR壓降方法,使用這種方法可以帶來非常穩健的內部電網結構。憑借強大的設計技術,該IR壓降方法能帶來出色的硅結果,單端口高速RAM上的8Kx72切口最低電壓可低至0.52V。

存儲器基本架構

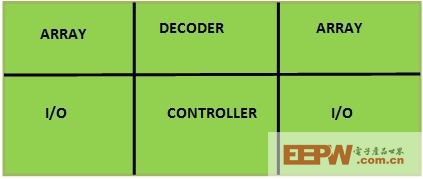

存儲器通常包含四個基本模塊——控制器、解碼器、陣列比特單元和輸入/輸出端。大部分吸收較多電流的大型驅動器都被置于輸入/輸出端、解碼器和控制模塊中。因此,為使各模塊正常運作,我們需要確保每個驅動器有足夠的電壓來保證正常運行。

存儲器基本模塊圖圖1:存儲器基本模塊圖

圖字:陣列;解碼器;陣列;輸入/輸出端;控制器;輸入/輸出端

系統芯片存儲器的連接指南

1.一般方法

一般地,存儲器所有者會以電網的捆扎頻率的形式向設計電源連接的SoC設計人員提供所有電源軌的指導大綱。捆扎頻率定義了給定電源線上的兩個連續金屬帶(一般在頂端金屬)之間的距離。在建造電網時按照捆扎指導大綱操作,可確保幾乎所有驅動器可獲得足夠的工作電壓,實現良好的性能。

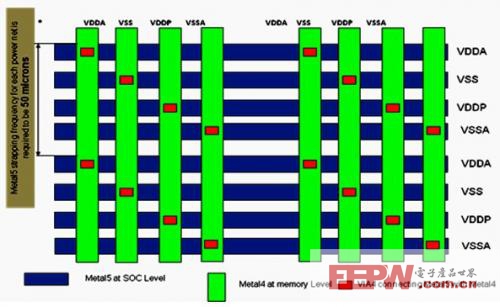

在圖2中,M4的供電軌是垂直的,應與水平的M5相連接。目標存儲器中存在著多個電源域,如VSSA、VDDP、VSS和VDDA等等。

圖2:系統芯片的電源連接結構圖

圖字:要求每個電源網的金屬5捆扎頻率為50微米;系統芯片級金屬5;存儲器級金屬4;VIA4將金屬5與金屬4相連接

將捆扎頻率作為唯一決定因素會導致的問題

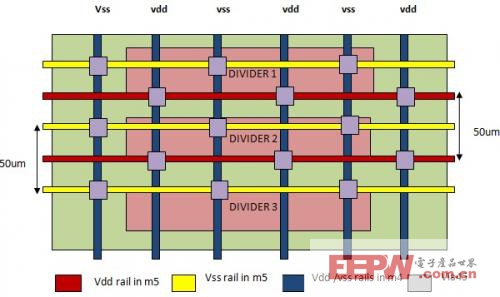

假設對于某項特定的技術,規定了一個50um的捆扎頻率。也就是說,每隔50um就應當重復電源線以確保恰當的功能和輸出。在這種情況下,只有一個電源線的驅動(VDD、VSS)是受IR壓降影響最嚴重的,因此這些裝置可能會出現異常行為。

在圖3中,分頻器3和分頻器1只分到一根VDD/VSS電源線,因此可能無法獲得足夠的電壓來確保正常的運作。此處,分頻器2有多個電源線,因而可以正常運行。

在單塊存儲器中,僅僅使用strapping技術也許足以確保正常的運行。然而,對于多組架構的儲存器或較長、較寬的存儲器而言,僅僅使用strapping技術是不足以實現IR壓降要求的。因此,在這種情況下,除了strapping之外,我們還需要使用其他方法來幫助我們實現IR的壓降目標。

圖3:長型存儲器的電源連接

圖字:分頻器1;分頻器2;分頻器3;M5上的Vdd導軌;M5上的VSS導軌;M4上的VDD/VSS

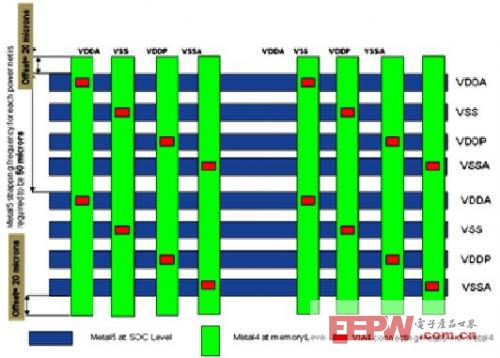

2.建議方法

為了使這些器件(分頻器)能夠正常運作,應當引入偏移量的概念,并且應當在整個存儲器編譯器進行IR壓降分析,包括所有可能的組合(如冗余、源偏置、DVFS和BIST等等)。下面將對以上概念進行詳細說明。此處偏移量被定義為頂層金屬的第一電源線和內存實例頂部之間的距離;或頂層金屬的最后一跟電源線和內存實例底部之間的距離。因此,在制作存儲器電網時,同時利用偏移量和strapping的概念可以改善IR的壓降水平。

圖4:20微米偏移量的電源連接

選擇合適的偏移值

按照規定,偏移值應該總是比捆扎頻率要少得多。這樣的偏移值可以確保某個給定內存塊中的所有分頻器都能有一個以上的電源線,從而獲得足夠的正常運行所需的電壓。

下面討論的一種方法可以用來為某個給定的存儲器選擇正確的捆扎頻率和偏移值。

如何確定捆扎頻率

情況1:連續的控制電源/接地導軌。

第1步:對各種捆扎頻率進行IR壓降分析,直到IR壓降在IO區停止。應將該頻率作為SFIO.

第2步:繼續分析IR壓降直到IR壓降在管制區內停止。應將該頻率作為SFCO.

第3步:實際捆扎頻率= SF =最小值(SFIO,SFCO)。

情況2:非連續的控制電源/接地導軌。

第1步:對各種捆扎頻率進行IR壓降分析,直到IR壓降在IO區無法繼續。應將該頻率作為SFIO.

第2步:繼續該分析直到IR壓降在管制區內停止。其中,電源strapping線在控制區以外運行,到達不連續的存儲器電源線的末端,以找到控制區捆扎頻率的最大可能值。應將該頻率作為SFCO.

第3步:實際捆扎頻率= SF =最小值(SFIO,SFCO)。

評論