基于DSP的合成孔徑雷達成像系統逆存儲轉置器設計

1.引言

合成孔徑雷達成像系統是一種全天時、全天候的高分辨率主動微波遙感成像系統,在地理遙感、地形測繪、災情預測和軍事偵察等領域有著重要應用。逆存儲轉置器(ICTM)是合成孔徑雷達成像系統的一個重要模塊,它需要將上位機方位壓縮模塊輸出的圖像數據以方位線的形式依次寫入外部存儲器,通過數據的逆轉置處理,以距離線的形式將圖像數據依次輸出。此外,ICTM的輸出數據將經過數據I/O節點發送到下位機圖像顯示模塊,使圖像顯示模塊能實時的以距離線形式滾動顯示雷達圖像。ICTM以TI的一款高性能定點DSP芯片TMS320C6415為核心處理器,兩條大容量SDRAM作為外部存儲器,實現輸入數據的逆存儲轉置操作,同時其強大的處理能力也為今后處理更多的數據提供了升級空間。

2.TMS320C6415芯片簡介

TMS320C6415是TI公司生產的高性能定點DSP C6000系列中的一款,該系列的DSP都是基于VelociTITM架構的VLIW DSP,在每個時鐘周期內可以執行8條32bit的指令。C6415的核心工作頻率最高可以達到720MHz,峰值工作速率為5.76GIPS。C6415提供與SDRAM的無縫接口,可以有效的簡化硬件設計開發難度,利用C6415的片選空間映射管理SDRAM,最多可以支持1GB的外部存儲空間,完全可以滿足逆存儲轉置處理所需的192M存儲要求。

TMS320C6415的CPU結構具有2個通道,每個通道有4個功能單元(1個乘法器和3個算術邏輯單元),16個32位通用寄存器,每個通道的功能單元可以隨意訪問本通道的寄存器。CPU還有2個交叉單元,通過它們,一個通道的功能單元可以訪問另一個通道的寄存器。另外,CPU還具有256bit寬的數據和程序通道,可以使程序寄存器在每個時鐘周期提供8條并行執行指令,這種CPU結構是DSP具有VLIW結構的基本條件。

DSP的存儲空間映射為內部存儲器、內部外設及外部擴展存儲器,其中內部存儲器由64KB內部程序存儲器和數據存儲器構成。內部程序存儲器可以映射到CPU地址空間或者作為Cache操作。內部和外部數據存儲器均可以通過CPU、DMA或HPI(Host Interface)方式訪問,HPI接口使上位機可以訪問DSP的存儲空間。

3.ICTM工作原理

ICTM模塊的主要功能是將上位機方位壓縮模塊輸出的數據重新排列順序,使得依次沿方位向排列的數據變換成沿距離向排列,使下位機圖像顯示模塊能實時滾動顯示圖像。

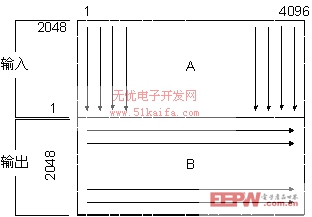

圖1 ICTM模塊工作原理示意圖

ICTM模塊的工作原理可用圖1來表示。整個SDRAM存儲空間劃分為BANKA和BANKB兩塊存儲區,兩塊BANK的列深度為輸入的方位向點數2048點,行深度為輸出的距離向點數4096點,為使兩塊BANK的讀/寫數據量平衡,需要在每個工作周期內輸入兩條方位線(2×2048點)數據,同時輸出一條距離線(1×4096點)數據。兩塊存儲區采用“乒乓”操作的讀寫方式,即如果等間隔讀BANKA區域,則連續寫BANKB區域,反之如果連續寫BANKA區域,則等間隔讀BANKB區域,讀完一塊存儲區的同時,另一塊存儲區也剛好寫滿。這樣兩塊存儲區交替工作,充分節約了讀/寫SDRAM的時間開銷,有利于滿足整個系統的實時性要求。

4.ICTM硬件電路設計

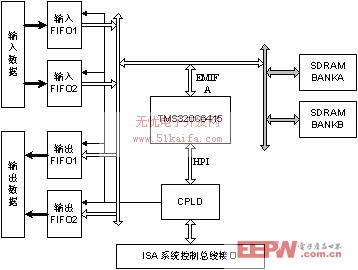

圖2 ICTM模塊硬件電路結構示意圖

ICTM模塊的硬件電路設計框圖如圖2所示。根據ICTM模塊的工作需要,主存儲器采用兩頁式工作結構,每頁集成256MBytes大小的SDRAM,分別配置在C6415的兩個CE空間。SDRAM和作為輸入/輸出緩存的同步FIFO都連接在C6415 64Bit位寬的EMIFA接口,以保證較高的數據傳輸帶寬。

4.1 SDRAM存儲電路

主存儲器類型選擇為SDRAM,即標準的144pin筆記本內存條(標準SODIMM封裝),目前選用256M容量大小。由于ICTM模塊的SDRAM接口采用可擴充接法,因此可以擴充到512MB容量。即如果SDRAM Module的容量為256MB,則列地址為A0~A8 ,如果SDRAM Module容量為512MB,則列地址為A0~A9。DSP的EMIFA口CE0、CE1輸出信號分別接SDRAM的BANK選擇管腳S0、S1。即如果SDRAM的BANK只有一個,則只有S0有效,這樣SDRAM只占用DSP的EMIFA口CE0空間,如果SDRAM的BANK有兩個,則占用DSP的EMIFA口CE0、CE1空間。

4.2 輸入/輸出FIFO

DSP的EMIFA口CE2/CE3空間分別控制輸入FIFO和輸出FIFO。輸入FIFO采用IDT公司的IDT72V3670(8K×36Bit),輸出FIFO采用IDT公司的IDT72V3680(16K×36 Bit),封裝形式為TQFP,128pin。FIFO的設計采用同步方式讀寫,但是利用0Ω電阻等效的短接線設計方式,也可以工作在異步模式下,FIFO控制信號通過CPLD做譯碼。

ICTM模塊用于讀寫操作的64bit FIFO采用用兩個32bit的FIFO并連實現,利用FIFO深度來做等效的輸入、輸出“乒乓”操作。其中輸出只用到一片FIFO,另外一片為將來大數據量的處理預留空間。

4.3 CPLD和HPI

ICTM模塊各功能單元的電路狀態、時序控制以及I/O接口控制都由CPLD完成。此外,通過C6415的主機接口(HPI)可以直接訪問DSP映射管理下的所有片內和片外存儲單元。因此,在電路設計中將DSP的HPI接口通過CPLD與系統控制總線相連,從而使主控能夠直接訪問DSP的HPI接口,進而滿足處理程序實時下載和指令數據實時傳輸的要求。

ICTM模塊的硬件設計充分考慮了結構化的設計要求,為合成孔徑雷達實時成像處理系統提供了高性能的逆存儲轉置硬件平臺,結合配置的控制軟件就可以實現實時成像處理所需的逆存儲轉置功能。

評論