基于ARM+FPGA的高速數據采集智能控制器設計

摘要:文章以嵌入式和數據采集技術為基礎,研究設計并實現了基于ARM+FPGA體系架構面向高速實時數據采集應用的一種實用新型智能控制器。本文闡述了主處理器ARM最小系統、協處理器FPGA最小系統和ARM與FPGA通信接口等硬件系統技術的實現,以及Linux FPGA字符設備驅動程序開發、協處理器FPGA控制程序和主處理器ARM應用程序設計。智能控制器運用FPGA并行運算處理結構的優勢,控制ADC進行高速數據采集。FPGA還可配置成軟核處理器-Nios II嵌入式處理器,與ARM構成雙核處理器系統。智能控制器通過ARM實現對FPGA的管理控制、實時數據采集和豐富外圍接口的通信。

本文引用地址:http://www.j9360.com/article/249568.htm0 引言

自上世紀七十年代初以來,微處理器的誕生促進了計算機信息技術的迅速發展和應用。數據采集與處理是集智能傳感器系統、信號采集調理與轉換、計算機信息等技術的綜合,是獲取信息的重要手段。隨著微處理器的普及,數據采集技術在工業領域中發揮著越來越重要的作用。

傳統的數據采集設備控制器主要是以單片機和PC機為主。前者處理數據運算能力有限、實時性較差;后者成本較高、靈活性差。ARM微處理器具有體積小、成本低,功能豐富等優點。FPGA并行運算結構,I/O資源豐富,在高速實時數據處理方面優勢明顯。采用ARM+FPGA的系統架構,可以綜合兩者優勢,實現數據高速實時采集與處理。

ARM與FPGA工作方式為主從模式。主處理器ARM選用美國ATMEL公司的AT91SAM9260,主頻工作在180MHz時可達200MIPS的處理性能。協處理

器選用的FPGA是Altera Cyclone系列EP1C6Q240I8NFPGA。FPGA工作時鐘是50MHZ,可以通過設置內部鎖相環使工作時鐘倍頻。

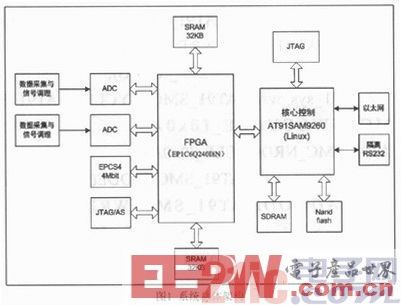

1 系統總體方案

智能控制器主要由ADC數據采集電路、FPGA最小系統、ARM最小系統三個部分構成。ADC選用單電源供電的14位的AD9240,采樣率可達10 MSPS。它采用高速、低成本的CMOS工藝,分辨率和速度均達到現有混合方案的水平,而功耗與成本卻低得多。協處理器選用ALTERA公司的EP1C6O240I8N芯片,通過外接兩片32KB SRAM存儲器、4Mbit串行配置芯片EPCS4、標準AS編程接口、JTAG調試接口構成FPGA最小系統。ARM最小系統由AT91SAM9260微處理器、運行和存儲程序的1片64MBytes的SDRAM和1片256 MBytes的NandFlash、1個RS232接口和1個10/100-Base-T以太網接口構成。

系統工作原理是:首先將信號采集調理電路過來的兩路信號分別送入兩個ADC同步采樣,ADC把模擬信號轉化為14bit精度的數字信號;然后FPGA對兩個通道的ADC轉換后的數字信號進行預處理,采用多點采樣求平均方法濾除50Hz工頻干擾;最后把兩個ADC采樣數據存儲到兩片SRAM緩存中。ARM與FPGA通信采用數據總線方式,通過在Linux操作系統下開發字符型FPGA設備驅動程序,然后編譯或者加載到Linux內核中,ARM可以在應用層程序讀取FPGA預處理后的數據,此時FPGA內部直接把ARM的總線連接到SRAM的總線上來讀取FPGA預處理后的數據。ARM可以通過以太網和RS232接口與上位機通信。

2 ARM和FPGA通信接口設計

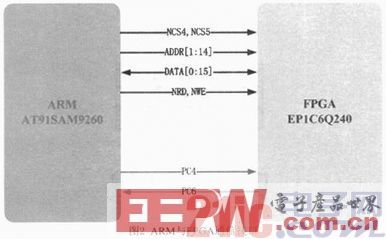

主處理器ARM所在的核心板負責整個系統的控制與管理。智能控制器與上位機的通信接口串口、以太網、CAN由此板引出。核心板與擴展板協處理器FPGA的通信采用總線方式。這種通信方式的本質是FPGA作為ARM的外設SRAM,ARM訪問存儲器,進行讀和寫操作。連接如圖2所示。

ARM與FPGA通過總線相連,ARM的數據線D0:D15、地址線A1:A14和片選NCS4、NCS5與FPGA相連,另外2片SRAM直接與FPGA相連。NCS4控制讀寫FPGA內部狀態寄存器和命令寄存器。NCS5控制FPGA讀寫兩片SRAM中存放的數據。所有數據信息都通過DATA[0:15]雙向數據總線傳輸。

NCS4片選有效對應ARM的地址映射為0X5000 0000-0X5000 8000,NCS5片選有效地址對應ARM的地址映射為0x60000000-0x6000 8000,FPGA此時實質上相當于ARM內部存儲器。在地址范圍內任意選取地址作為ARM與FPGA通信的FPGA內部寄存器地址。這些寄存器有ARM向FPGA內部寫寄存器,也有ARM從FPGA內部讀寄存器。

主處理器ARM要想從0X6000 0000-0x6000 8000地址范圍內直接讀出兩片SRAM中存儲的ADC采樣預處理后的的數據,需要有協處理器FPGA的協助配合。

這樣就明確了協處理器FPGA在與主處理器ARM通信時需要完成的任務:1)解析主處理器ARM寫FPGA寄存器的命令,執行相應操作;2)將執行操作后的一些狀態信息寫入相應的FPGA內部寄存器供主處理器查詢操作結果:3)協助配合主處理器ARM讀取兩片SRAM中存儲的ADC采集預處理后的數據。

3 系統軟件設計

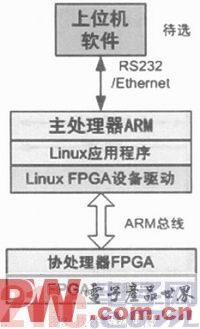

智能控制器軟件包括Linux FPGA字符型設備驅動程序、主處理器ARM應用程序、FPGA數據釆集及預處理存儲程序。軟件系統結構框圖如圖3所示。

3.1 FPGA設備驅動程序

Linux設備驅動被分為三類:字符設備、塊設備和網絡設備。字符設備是以字符為單位輸入輸出數據的設備。FPGA設備驅動程序為字符型設備驅動程序,其基本框架為:1)定義一個結構體static structfile operations變量,其內定義一些設備的打開、關閉、讀、寫、控制函數;2)在結構體外分別實現結構體中定義的這些函數;3)向內核中注冊或刪除驅動模塊。Linux內核中一個字符設備用cdev數據結構來描述和管理設備文件。智能控制器的協處理器FPGA用作主處理器ARM外部靜態存儲器SRAM。因此,主處理器ARM可以通過靜態存儲控制器(SMC)產生信號控制外部存儲設備或者外圍接口設備來進行讀寫操作。FPGA字符型設備驅動程序能夠完成控制FPGA模塊,完成數據采集,最為關鍵的是初始化FPGA模塊,配置主處理器ARM的SMC來實現FPGA總線驅動。可參照ARM靜態存儲控制器讀、寫時序。

linux操作系統文章專題:linux操作系統詳解(linux不再難懂)

fpga相關文章:fpga是什么

linux相關文章:linux教程

鎖相環相關文章:鎖相環原理

評論