基于TMS320VC5416的自適應變速率聲碼器

清華大學自主開發的正弦激勵線性預測(SELP)系列低速率語音編碼算法由于采用了合理的激勵模型,在2.4kbps、1.2kbps和0.6kbps三個速率上都具有很好的重建語音質量。其中,2.4kbps速率算法的重建語音質量與國際上流行的相同速率的高質量AMBE算法相當,0.6kbps算法重建語音的可懂度也能達到90%以上,十分適合應用在各種軍用語音通信系統中。 本文詳細介紹了利用TMS320VC5416 DSP實現的自適應變速率SELP聲碼器。該聲碼器可根據不同的速率要求自動實時地切換到不同速率的算法進行語音通信,具有很好的通用性和靈活性。

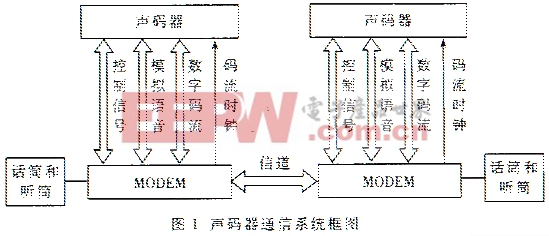

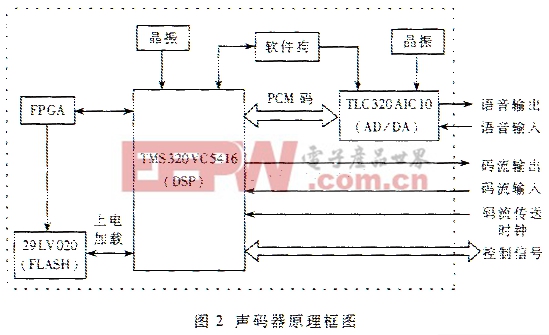

清華大學自主開發的正弦激勵線性預測(SELP)系列低速率語音編碼算法由于采用了合理的激勵模型,在2.4kbps、1.2kbps和0.6kbps三個速率上都具有很好的重建語音質量。其中,2.4kbps速率算法的重建語音質量與國際上流行的相同速率的高質量AMBE算法相當,0.6kbps算法重建語音的可懂度也能達到90%以上,十分適合應用在各種軍用語音通信系統中。 本文詳細介紹了利用TMS320VC5416 DSP實現的自適應變速率SELP聲碼器。該聲碼器可根據不同的速率要求自動實時地切換到不同速率的算法進行語音通信,具有很好的通用性和靈活性。 1 聲碼器系統的結構和原理 聲碼器通信系統是建立在通用的MODEM平臺上的,可以按照2.4kbps、1.2kbps和0.6kbps中的任一個速率實現全雙工語音通信。圖1為整個通信系統的原理框圖。 MODEM平臺負責對數字碼流進行調制解調和通信,聲碼器則負責按照MODEM的要求對語音進行編解碼。MODEM把話筒提供的模擬語音送給聲碼器編碼并將聲碼器的解碼語音送給聽筒。MODEM還負責給聲碼器提供碼流傳送時鐘,聲碼器則按照這個時鐘與MODEM交換數字碼流。另外,MODEM和聲碼器之間還有一些控制信號線用來彼此交換狀態信息。表1是MODEM和聲碼器之間的主要接口關系。表1 MODEM和聲碼器的主要接口 名 字方 向功 能 AinMODEM至聲碼器模擬語音輸入Aout聲碼器至MODEM模擬語音輸出CLKMODEM至聲碼器碼流傳送時鐘,聲碼器按照CLK的頻率進行編解碼TXD聲碼器至MODEM聲碼器至MODEM的數據線,在CLK的下降沿有效RXDMODEM至聲碼器MODEM至聲碼器的數據線,在CLK的上升沿有效PTTMODEM至聲碼器PCM碼有效標志RTS聲碼器至MODEM發送碼流有效標志CDMODEM至聲碼器接收碼流有效標志雖然MODEM可以根據網絡條件和外界要求自動改變速率,但是卻沒有專門的信號線用來通知聲碼器進行速率轉換。注意到碼流傳送時鐘CLK是根據速率要求實時變化的,所以聲碼器通過檢測CLK的頻率就可以得到當前的速率轉換信息。 聲碼器的核心部分是一片TMS320VC5416 DSP芯片,負責編解碼和控制工作。另外,還有一片TI公司生產的TLC320AIC10芯片,負責語音的數模/模數(AD/DA)轉換;一片FPGA,負責數字邏輯轉換;一片2Mbit容量的8位FLASH存儲器29LV020,負責存儲所有程序和數據并在上電時加載到DSP的片內RAM上。聲碼器還有一個軟件狗對系統工作狀態進行實時監控,并在需要時對整個聲碼器進行復位。圖2是聲碼器的原理框圖。 當MODEM需要聲碼器進行編碼時,它通過PTT信號通知聲碼器,并同時向聲碼器發送模擬語音信號。聲碼器利用其中的AD/DA芯片將其采樣量化為PCM數字信號送給DSP,DSP則根據MODEM提供的時鐘信號CLK的頻率選擇不同速率的編碼算法對輸入PCM信號進行編碼,然后把碼流通過TXD送回給MODEM,并同時通過RTS信號通知MODEM碼流有效,MODEM就可以將碼流進行調制并發送。接收時,

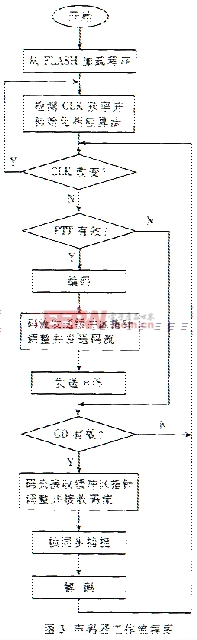

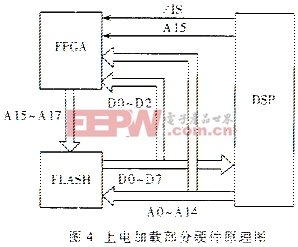

1 聲碼器系統的結構和原理 聲碼器通信系統是建立在通用的MODEM平臺上的,可以按照2.4kbps、1.2kbps和0.6kbps中的任一個速率實現全雙工語音通信。圖1為整個通信系統的原理框圖。 MODEM平臺負責對數字碼流進行調制解調和通信,聲碼器則負責按照MODEM的要求對語音進行編解碼。MODEM把話筒提供的模擬語音送給聲碼器編碼并將聲碼器的解碼語音送給聽筒。MODEM還負責給聲碼器提供碼流傳送時鐘,聲碼器則按照這個時鐘與MODEM交換數字碼流。另外,MODEM和聲碼器之間還有一些控制信號線用來彼此交換狀態信息。表1是MODEM和聲碼器之間的主要接口關系。表1 MODEM和聲碼器的主要接口 名 字方 向功 能 AinMODEM至聲碼器模擬語音輸入Aout聲碼器至MODEM模擬語音輸出CLKMODEM至聲碼器碼流傳送時鐘,聲碼器按照CLK的頻率進行編解碼TXD聲碼器至MODEM聲碼器至MODEM的數據線,在CLK的下降沿有效RXDMODEM至聲碼器MODEM至聲碼器的數據線,在CLK的上升沿有效PTTMODEM至聲碼器PCM碼有效標志RTS聲碼器至MODEM發送碼流有效標志CDMODEM至聲碼器接收碼流有效標志雖然MODEM可以根據網絡條件和外界要求自動改變速率,但是卻沒有專門的信號線用來通知聲碼器進行速率轉換。注意到碼流傳送時鐘CLK是根據速率要求實時變化的,所以聲碼器通過檢測CLK的頻率就可以得到當前的速率轉換信息。 聲碼器的核心部分是一片TMS320VC5416 DSP芯片,負責編解碼和控制工作。另外,還有一片TI公司生產的TLC320AIC10芯片,負責語音的數模/模數(AD/DA)轉換;一片FPGA,負責數字邏輯轉換;一片2Mbit容量的8位FLASH存儲器29LV020,負責存儲所有程序和數據并在上電時加載到DSP的片內RAM上。聲碼器還有一個軟件狗對系統工作狀態進行實時監控,并在需要時對整個聲碼器進行復位。圖2是聲碼器的原理框圖。 當MODEM需要聲碼器進行編碼時,它通過PTT信號通知聲碼器,并同時向聲碼器發送模擬語音信號。聲碼器利用其中的AD/DA芯片將其采樣量化為PCM數字信號送給DSP,DSP則根據MODEM提供的時鐘信號CLK的頻率選擇不同速率的編碼算法對輸入PCM信號進行編碼,然后把碼流通過TXD送回給MODEM,并同時通過RTS信號通知MODEM碼流有效,MODEM就可以將碼流進行調制并發送。接收時, 也是由MODEM解調出碼流后按照CLK的頻率通過RXD發給聲碼器,并同時通過CD信號通知聲碼器碼流有效,聲碼器則對接收的碼流進行解碼,并利用AD/DA將解碼后的PCM語音轉換為模擬語音信號送回MODEM。據此就可以設計出聲碼器的工作流程,如圖3所示。 其中的幀同步捕捉指的是對接收到的碼流的分幀工作,因為SELP是基于幀結構的編解碼算法,所以在解碼之前需要先利用幀同步算法捕捉到每幀的起始位置。這里采用的是基于計數器的幀同步捕捉算法。 另外,由于聲碼器的碼流收發都是按照CLK頻率連續進行的,而基于幀結構的SELP編解碼器對碼流的輸入輸出卻是每幀進行一次的,所以對于發送和接收碼流都需要設置循環緩沖區并對每個緩沖區設置一讀一寫兩個指針。這兩個指針間的距離應大于一倍幀長。但由于聲碼器中給AD/DA提供采樣時鐘的晶振有一定誤差,所以導致這兩個指針移動速度不同。以輸入碼流緩沖區為例,其讀指針應由SELP編碼器控制,而編碼器被調用的頻率由本地晶振的頻率決定,所以讀指針的移動速度由本地晶振控制。寫指針則是由碼流輸入部分控制,其移動速度實際上是由對方的解碼速度決定的,也就是受對方聲碼器的晶振控制。所以在編碼后和解碼前都需要進行指針調整,也就是檢查碼流緩沖區的讀寫指針間距,并根據需要丟棄一幀或復制一幀。 聲碼器設計和實現中的主要難點在于硬件接口的設計和FLASH上電加載部分,下面分別進行介紹。 2 硬件接口的設計 TMS320VC5416片上有三個多通道緩沖串口(MCBSP),每個MCBSP都可以作為串口使用或被初始化成通用I/O口使用。其中,MCBSP0按照串口的工作方式與AD/DA相連,這部分比較簡單,按照典型的連接方式即可實現。但是碼流收發部分則不同,因為這部分只有一根同步時鐘線CLK和輸入輸出兩根數據線,所以很難直接利用MCBSP按串口方式實現收發。于是把MCBSP1初始化成通用I/O,將RXD與I/O口輸入腳DR1相連,TXD與I/O口的輸出腳DX1相連,將CLK與初始化為I/O口的輸入腳FSR1相連。這樣在程序中就可以很方便地隨時讀寫這三根信號線,再將時鐘中斷的頻率設為50kHz(遠高于CLK可能出現的最高頻率2.4kHz),就可以在時鐘中斷中實時監測CLK的變化。若發現CLK的上升沿則讀取RXD的狀態并存入碼流接收緩沖區,若發現CLK的下降沿則從碼流發送緩沖區取出1bit送至TXD。這樣就成功地實現了碼流的收發。 MCBSP1被初始化為通用I/O后一共能提供6根I/O引腳線,除去碼流收發占用的3根之外還有3根,正好可以用來連接PTT、RTS和CD信號線。這樣,就可以在占用最少的DSP資源的情況下實現碼流收發和控制功能。 另一個主要問題就是速率的自適應問題,也就是說,聲碼器必須能夠根據CLK的頻率自動選擇合適的編解碼算法。在上述連接方式下,這個問題也就很容易解決了,只需設立一個計數器,對CLK的每個周期中發生的時鐘中斷個數進行計數即可。這樣,根據計數值就可以很方便地計算出CLK的頻率。例如,時鐘中斷的頻率是50kHz,那么當CLK的頻率是2.4kHz時,計數器的值就應該在50/2.4=20.8左右,當CLK的頻率是1.2kHz時,則在41.7左右;當CLK的頻率是0.6kHz時,則在83.3左右。從圖2的流程中可以看出,在程序初始化前就需要檢測CLK頻率,并根據CLK的頻率選擇合適的編解碼算法,進行相應的初始化。在程序的執行過程中也要對CLK的頻率進行實時監測,若發現頻率改變就立即重新初始化聲碼器。這樣就能夠保證聲碼器實時地跟蹤CLK的變化,實現自適應速率切換。 對于軟件狗所需的周期變化信號,則通過DSP上的輸出引腳XF給出,并在程序中及時翻轉XF的電平得到。 3 上電加載部分(Bootload)的實現 TMS320VC5416 DSP片內ROM中有固化的自加載程序(Bootloader),但它對被加載程序的大小有限制。在使用8bit FLASH的情況下,只能加載小于16KWord的內容。而三個速率的SELP算法程序區和數據區的總數據量遠遠超過16KWord,顯然只使用DSP片內的Bootloader是不能滿足需要的。所以必須自己寫加載程序。首先由TMS320VC5416片內的Bootloader把自己寫的加載程序加載到片內RAM,然后執行這段加載程序,加載其它部分。這里需要解決的一個主要問題就是FLASH數據和DSP地址空間的映射關系。由于SELP算法的程序數據總量很大,所以必須用到片內擴展的程序區,也就是說MP/MC標志位需設為0。從此時的Memory Map中可以看出,DSP可以訪問的每塊連續片外地址空間只有32K,所以FLASH數據只能按照每頁32K的方式分頁映射到DSP地址空間。使用FPGA可以很方便地控制哪頁FLASH數據映射到DSP中,這部分的原理框圖如圖4所示。

也是由MODEM解調出碼流后按照CLK的頻率通過RXD發給聲碼器,并同時通過CD信號通知聲碼器碼流有效,聲碼器則對接收的碼流進行解碼,并利用AD/DA將解碼后的PCM語音轉換為模擬語音信號送回MODEM。據此就可以設計出聲碼器的工作流程,如圖3所示。 其中的幀同步捕捉指的是對接收到的碼流的分幀工作,因為SELP是基于幀結構的編解碼算法,所以在解碼之前需要先利用幀同步算法捕捉到每幀的起始位置。這里采用的是基于計數器的幀同步捕捉算法。 另外,由于聲碼器的碼流收發都是按照CLK頻率連續進行的,而基于幀結構的SELP編解碼器對碼流的輸入輸出卻是每幀進行一次的,所以對于發送和接收碼流都需要設置循環緩沖區并對每個緩沖區設置一讀一寫兩個指針。這兩個指針間的距離應大于一倍幀長。但由于聲碼器中給AD/DA提供采樣時鐘的晶振有一定誤差,所以導致這兩個指針移動速度不同。以輸入碼流緩沖區為例,其讀指針應由SELP編碼器控制,而編碼器被調用的頻率由本地晶振的頻率決定,所以讀指針的移動速度由本地晶振控制。寫指針則是由碼流輸入部分控制,其移動速度實際上是由對方的解碼速度決定的,也就是受對方聲碼器的晶振控制。所以在編碼后和解碼前都需要進行指針調整,也就是檢查碼流緩沖區的讀寫指針間距,并根據需要丟棄一幀或復制一幀。 聲碼器設計和實現中的主要難點在于硬件接口的設計和FLASH上電加載部分,下面分別進行介紹。 2 硬件接口的設計 TMS320VC5416片上有三個多通道緩沖串口(MCBSP),每個MCBSP都可以作為串口使用或被初始化成通用I/O口使用。其中,MCBSP0按照串口的工作方式與AD/DA相連,這部分比較簡單,按照典型的連接方式即可實現。但是碼流收發部分則不同,因為這部分只有一根同步時鐘線CLK和輸入輸出兩根數據線,所以很難直接利用MCBSP按串口方式實現收發。于是把MCBSP1初始化成通用I/O,將RXD與I/O口輸入腳DR1相連,TXD與I/O口的輸出腳DX1相連,將CLK與初始化為I/O口的輸入腳FSR1相連。這樣在程序中就可以很方便地隨時讀寫這三根信號線,再將時鐘中斷的頻率設為50kHz(遠高于CLK可能出現的最高頻率2.4kHz),就可以在時鐘中斷中實時監測CLK的變化。若發現CLK的上升沿則讀取RXD的狀態并存入碼流接收緩沖區,若發現CLK的下降沿則從碼流發送緩沖區取出1bit送至TXD。這樣就成功地實現了碼流的收發。 MCBSP1被初始化為通用I/O后一共能提供6根I/O引腳線,除去碼流收發占用的3根之外還有3根,正好可以用來連接PTT、RTS和CD信號線。這樣,就可以在占用最少的DSP資源的情況下實現碼流收發和控制功能。 另一個主要問題就是速率的自適應問題,也就是說,聲碼器必須能夠根據CLK的頻率自動選擇合適的編解碼算法。在上述連接方式下,這個問題也就很容易解決了,只需設立一個計數器,對CLK的每個周期中發生的時鐘中斷個數進行計數即可。這樣,根據計數值就可以很方便地計算出CLK的頻率。例如,時鐘中斷的頻率是50kHz,那么當CLK的頻率是2.4kHz時,計數器的值就應該在50/2.4=20.8左右,當CLK的頻率是1.2kHz時,則在41.7左右;當CLK的頻率是0.6kHz時,則在83.3左右。從圖2的流程中可以看出,在程序初始化前就需要檢測CLK頻率,并根據CLK的頻率選擇合適的編解碼算法,進行相應的初始化。在程序的執行過程中也要對CLK的頻率進行實時監測,若發現頻率改變就立即重新初始化聲碼器。這樣就能夠保證聲碼器實時地跟蹤CLK的變化,實現自適應速率切換。 對于軟件狗所需的周期變化信號,則通過DSP上的輸出引腳XF給出,并在程序中及時翻轉XF的電平得到。 3 上電加載部分(Bootload)的實現 TMS320VC5416 DSP片內ROM中有固化的自加載程序(Bootloader),但它對被加載程序的大小有限制。在使用8bit FLASH的情況下,只能加載小于16KWord的內容。而三個速率的SELP算法程序區和數據區的總數據量遠遠超過16KWord,顯然只使用DSP片內的Bootloader是不能滿足需要的。所以必須自己寫加載程序。首先由TMS320VC5416片內的Bootloader把自己寫的加載程序加載到片內RAM,然后執行這段加載程序,加載其它部分。這里需要解決的一個主要問題就是FLASH數據和DSP地址空間的映射關系。由于SELP算法的程序數據總量很大,所以必須用到片內擴展的程序區,也就是說MP/MC標志位需設為0。從此時的Memory Map中可以看出,DSP可以訪問的每塊連續片外地址空間只有32K,所以FLASH數據只能按照每頁32K的方式分頁映射到DSP地址空間。使用FPGA可以很方便地控制哪頁FLASH數據映射到DSP中,這部分的原理框圖如圖4所示。 FLASH的低15根地址線A0~A14直接接到DSP上,而高3根地址線A15~A17則由FPGA控制。在DSP向I/O空間的特定地址寫數時,FPGA內部的邏輯電路就會將D0~D2(也就是所寫數據的低3位)鎖存到A15~A17上。這樣就實現了軟件控制FLASH數據映射關系的功能。再把所有的數據進行合理的劃分和排列,燒入FLASH中,就可實現全部程序的自加載。 由于采用獨特的硬件接口方式,很方便地實現了自適應變速率的功能,大大提高了聲碼器的靈活性和適用范圍。TMS320VC5416擁有很大的片內RAM,本文提出的使用FPGA輔助完成大數據量程序上電自加載的方法對于TMS320VC5416的其它應用場合也同樣適用。 使用以上方法實現的自適應變速率SELP聲碼器在TMS320VC5416上占用的硬件資源情況如表2所示。表2 硬件資源占用情況 運算量(峰值)(MIPS)存儲量(KWords)程序區數據區公共單獨2.4kbps算法43.011.411.65.41.2kbps算法52.425.00.6kbps算法35.427.4總運算量=MAX(43.0,52.4,35.4)=52.4MIPS 總存儲量=11.4+11.6+5.4+25.0+27.4=80.8KWord 該聲碼器已在實際通信系統中獲得應用并表現出了很好的性能。

FLASH的低15根地址線A0~A14直接接到DSP上,而高3根地址線A15~A17則由FPGA控制。在DSP向I/O空間的特定地址寫數時,FPGA內部的邏輯電路就會將D0~D2(也就是所寫數據的低3位)鎖存到A15~A17上。這樣就實現了軟件控制FLASH數據映射關系的功能。再把所有的數據進行合理的劃分和排列,燒入FLASH中,就可實現全部程序的自加載。 由于采用獨特的硬件接口方式,很方便地實現了自適應變速率的功能,大大提高了聲碼器的靈活性和適用范圍。TMS320VC5416擁有很大的片內RAM,本文提出的使用FPGA輔助完成大數據量程序上電自加載的方法對于TMS320VC5416的其它應用場合也同樣適用。 使用以上方法實現的自適應變速率SELP聲碼器在TMS320VC5416上占用的硬件資源情況如表2所示。表2 硬件資源占用情況 運算量(峰值)(MIPS)存儲量(KWords)程序區數據區公共單獨2.4kbps算法43.011.411.65.41.2kbps算法52.425.00.6kbps算法35.427.4總運算量=MAX(43.0,52.4,35.4)=52.4MIPS 總存儲量=11.4+11.6+5.4+25.0+27.4=80.8KWord 該聲碼器已在實際通信系統中獲得應用并表現出了很好的性能。

評論