PCI總線和DSP芯片的圖像處理平臺的硬件設計

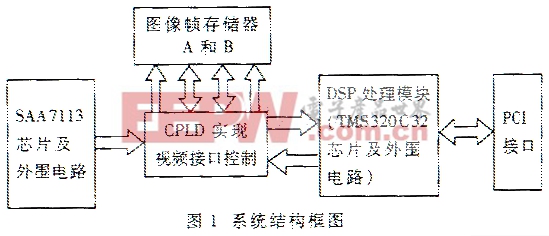

1 系統功能概述 根據實際應用需要,該系統的主要功能有: (1)可以在不同輸入制式PAL和NTSC之間進行自動切換和處理。 (2)能利用采集到的YUV圖像信號數據進行壓縮算法的驗證,或轉換成灰度圖像數據、RGB格式圖像數據等進行檢測、定位等算法的檢驗。 (3)能將處理后的數據通過PCI接口交給上層系統(PC機)保存或進行進一步驗證處理。 (4)系統具有軟件修改、升級功能和靈活性,便于算法的改進驗證。 系統的設計難點主要是如何實現系統數據的高速傳輸。圖像數據由專用集成視頻解碼器SAA7113采集,經A/D轉換處理后傳輸到DSP;再經DSP處理后通過PCI接口傳輸到PC機。如何實現SAA7113與DSP之間和DSP與S5933之間的高效率數據通信是解決這個問題的關鍵。通過分析研究,在SAA7113與DSP之間采用CPLD控制的兩幀輪換方式,實現圖像的隔行信號變逐行信號以及采集和處理的同步進行;在DSP與S5933之間采用DMA傳輸方式,實現數據流在系統中的高速傳輸,以滿足圖像處理要求。 2 系統的硬件設計 整個系統由視頻解碼器、DSP和PCI總線專用芯片組成。系統框圖如圖1所示。 DSP芯片采用TMS320C32,該芯片是在TMS320C30的基礎上簡化而來的,含有TMS320C30 CPU核心。它增加了一些常用的功能部件,使程序引導功能、串行接口傳輸和存儲器均可支持8、16、32位的數據。它可產生邊沿中斷和電平中斷,可由用戶編程設定中斷向量表的地址,具有空等待和低功耗兩種電源管理方式。它具有兩個DMA通道,功能強大的外部存儲器接口既可以滿足視頻解碼接口8位數據的要求,也可以實現PCI接口32位數據的的高速數據傳輸。TMS320C32靈活的程序加載可以實現在系統編程。

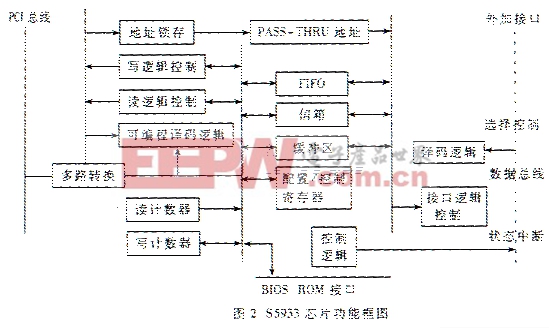

1 系統功能概述 根據實際應用需要,該系統的主要功能有: (1)可以在不同輸入制式PAL和NTSC之間進行自動切換和處理。 (2)能利用采集到的YUV圖像信號數據進行壓縮算法的驗證,或轉換成灰度圖像數據、RGB格式圖像數據等進行檢測、定位等算法的檢驗。 (3)能將處理后的數據通過PCI接口交給上層系統(PC機)保存或進行進一步驗證處理。 (4)系統具有軟件修改、升級功能和靈活性,便于算法的改進驗證。 系統的設計難點主要是如何實現系統數據的高速傳輸。圖像數據由專用集成視頻解碼器SAA7113采集,經A/D轉換處理后傳輸到DSP;再經DSP處理后通過PCI接口傳輸到PC機。如何實現SAA7113與DSP之間和DSP與S5933之間的高效率數據通信是解決這個問題的關鍵。通過分析研究,在SAA7113與DSP之間采用CPLD控制的兩幀輪換方式,實現圖像的隔行信號變逐行信號以及采集和處理的同步進行;在DSP與S5933之間采用DMA傳輸方式,實現數據流在系統中的高速傳輸,以滿足圖像處理要求。 2 系統的硬件設計 整個系統由視頻解碼器、DSP和PCI總線專用芯片組成。系統框圖如圖1所示。 DSP芯片采用TMS320C32,該芯片是在TMS320C30的基礎上簡化而來的,含有TMS320C30 CPU核心。它增加了一些常用的功能部件,使程序引導功能、串行接口傳輸和存儲器均可支持8、16、32位的數據。它可產生邊沿中斷和電平中斷,可由用戶編程設定中斷向量表的地址,具有空等待和低功耗兩種電源管理方式。它具有兩個DMA通道,功能強大的外部存儲器接口既可以滿足視頻解碼接口8位數據的要求,也可以實現PCI接口32位數據的的高速數據傳輸。TMS320C32靈活的程序加載可以實現在系統編程。 PCI總線專用接口芯片采用S5933,它是一種功能強且使用靈活的PCI總線控制器專用芯片,該芯片符合PCI局部總線規范2.1版本,既可作為PCI總線目標設備,實現基本的傳送要求;也可作為PCI總線主控設備,訪問其它PCI總線設備。S5933的峰值傳送速率為132Mbps(32位PCI數據線)。S5933提供了3個物理總線接口:PCI總線接口、外加總線接口(ADD-ON BUS);可選的NV存儲器接口。用戶可根據需要設計S5933與外加總線接口相連接的邏輯電路和配置空間的初始化,而不必考慮PCI總線規范眾多的協議,從而將復雜的PCI總線接口關系轉化為簡單的8/16/32位外加總線(ADD-ON BUS)接口關系。S5933芯片功能框圖如圖2所示。 PCI總線與外加總線之間的數據傳輸可以通過內部先入先出存儲器(FIFO)、郵箱寄存器(Mailbox)和數據直傳通道(Pass-Thru)三種通道進行。各通道都包括兩組寄存器以分別完成PCI總線和ADD-ON總線接口雙向數據傳輸,為使用者提供較為寬松而靈活的設計空間。 可編程視頻解碼芯片采用SAA7113;該芯片是可編程視頻處理芯片,采用CMOS工藝。通過簡單的I2C總線可以對其實現編程控制;內部包含兩路模擬處理通道,能實現視頻源的選擇、抗混疊(去假頻)濾波、模/數變換、自動嵌位、自動增益控制、時鐘產生、多制式(PAL BGHI、PAL M、PAL N、NTSC M和NTSC N)解碼及亮度、對比度和飽和度控制。 本系統采用軟件模擬I2C總線的控制方式,通過DSP的多功能口實現DSP對SAA7113的初始化等控制;根據SAA7113輸出的同步脈沖,通過使用可編程器件CPLD,產生圖像幀存儲器的地址信號、讀寫信號以及幀切換等控制信號,實現SAA7113和DSP之間的高速數據通訊。 3 DSP與SAA7113之間的無縫連接 SAA7113輸出的是隔行視頻信號,一幀圖像需要傳送兩次,分別記為奇場圖像和偶場圖像;視頻處理的對象是逐行排列的圖像信號,因此必須等待一幀圖像(連續的奇、偶兩場信號)采集完后,合成到一個圖像幀中才能進行后續處理。利用SAA7113的同步信號,使用可編程邏輯器件CPLD構建控制器,可將圖像數據寫入幀存儲器,解決圖像幀合成問題。為了向前端處理器(DSP)提供連續的圖像信號,采用兩個圖像幀存儲器A和B交替存儲的方式,來暫存采集到的圖像數據和需要處理的圖像數據,可實現圖像的實時連續采集處理。

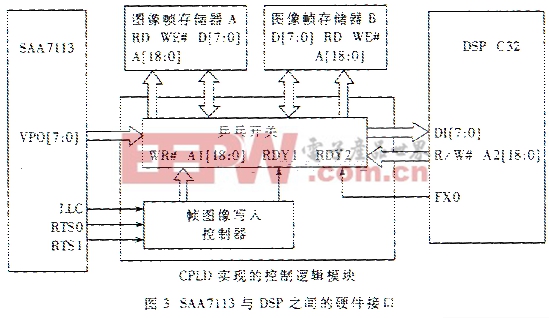

PCI總線專用接口芯片采用S5933,它是一種功能強且使用靈活的PCI總線控制器專用芯片,該芯片符合PCI局部總線規范2.1版本,既可作為PCI總線目標設備,實現基本的傳送要求;也可作為PCI總線主控設備,訪問其它PCI總線設備。S5933的峰值傳送速率為132Mbps(32位PCI數據線)。S5933提供了3個物理總線接口:PCI總線接口、外加總線接口(ADD-ON BUS);可選的NV存儲器接口。用戶可根據需要設計S5933與外加總線接口相連接的邏輯電路和配置空間的初始化,而不必考慮PCI總線規范眾多的協議,從而將復雜的PCI總線接口關系轉化為簡單的8/16/32位外加總線(ADD-ON BUS)接口關系。S5933芯片功能框圖如圖2所示。 PCI總線與外加總線之間的數據傳輸可以通過內部先入先出存儲器(FIFO)、郵箱寄存器(Mailbox)和數據直傳通道(Pass-Thru)三種通道進行。各通道都包括兩組寄存器以分別完成PCI總線和ADD-ON總線接口雙向數據傳輸,為使用者提供較為寬松而靈活的設計空間。 可編程視頻解碼芯片采用SAA7113;該芯片是可編程視頻處理芯片,采用CMOS工藝。通過簡單的I2C總線可以對其實現編程控制;內部包含兩路模擬處理通道,能實現視頻源的選擇、抗混疊(去假頻)濾波、模/數變換、自動嵌位、自動增益控制、時鐘產生、多制式(PAL BGHI、PAL M、PAL N、NTSC M和NTSC N)解碼及亮度、對比度和飽和度控制。 本系統采用軟件模擬I2C總線的控制方式,通過DSP的多功能口實現DSP對SAA7113的初始化等控制;根據SAA7113輸出的同步脈沖,通過使用可編程器件CPLD,產生圖像幀存儲器的地址信號、讀寫信號以及幀切換等控制信號,實現SAA7113和DSP之間的高速數據通訊。 3 DSP與SAA7113之間的無縫連接 SAA7113輸出的是隔行視頻信號,一幀圖像需要傳送兩次,分別記為奇場圖像和偶場圖像;視頻處理的對象是逐行排列的圖像信號,因此必須等待一幀圖像(連續的奇、偶兩場信號)采集完后,合成到一個圖像幀中才能進行后續處理。利用SAA7113的同步信號,使用可編程邏輯器件CPLD構建控制器,可將圖像數據寫入幀存儲器,解決圖像幀合成問題。為了向前端處理器(DSP)提供連續的圖像信號,采用兩個圖像幀存儲器A和B交替存儲的方式,來暫存采集到的圖像數據和需要處理的圖像數據,可實現圖像的實時連續采集處理。 DSP與SAA7113之間的硬件接口如圖3所示,整個接口的控制邏輯,包括兩個子模塊:幀圖像寫入控制器和乒乓開關,由一塊CPLD來完成。CPLD芯片采用ALTERA公司的EPM9320RC208。兩組幀存儲器A和B采用CYPRESS公司生產的兩塊CY7C1049芯片,容量為512K%26;#215;8bit,存取時間不超過15ns,能滿足圖像實時采集要求。 SAA7113由數字視頻輸出口VPO?眼7:0,輸出視頻數據。系統設置SAA7113的輸出數據為標準的ITU 656 4?押2?押2 YUV格式,每一個象素的數據由兩個連續的字節表示。為了方便地存儲處理圖像,系統僅取一幀圖像中間的512%26;#215;512個象素作為一幀,即所取圖像幀為連續奇偶兩場圖像的中央512行,且每行取中間的512個象素的圖像塊。 利用SAA7113的同步信號,幀圖像寫入控制器模塊產生幀存儲器的地址信號、寫信號以及幀切換信號之一(RDY1)。SAA7113輸出的同步信號包括LLC、RTS0、RTS1。LLC是行鎖定系統時鐘輸出,為象素時鐘頻率的兩倍,即27MHz,用來同步數據采集,使得一個LLC周期輸出一個字節的圖像數據。在圖像數據有效時,其上升沿反相后作為幀存儲器的WE#信號。RTS0、RTS1的功能是通過編程設置SAA7113功能寄存器確定的。RTS0被設置為水平輸出參考信號(行有效信號),RTS0高電平時表示采集一行有效象素,低電平時表示場消隱信號?熏在RTSO上升沿后,幀圖像寫入控制器控制采集一行中間的512個象素數據,將其余的象素數據丟棄。RTS1被設置為垂直輸出參考信號和奇偶場信號,RTS1高電平時表示采集奇場圖像所需要的有效數據,在RTS1上升沿時,開始采集奇場圖像數據,同時它也被用來作為幀圖像開始的信號;RTS1低電平時表示采集偶場中所需要的圖像數據,在RTS1下降沿時,開始采集偶場圖像數據。在RTS1上升沿時,幀圖像寫入控制器控制采集256行象素數據作為奇場圖像;在RTS1下降沿時,順次采集下面的256行象素數據作為偶場圖像,其余的圖像行數據丟棄。使用512K%26;#215;8bit的靜態存儲器(SRAM),恰好可以存放一幀512%26;#215;512%26;#215;2%26;#215;8bit的圖像。在合成一幀圖像時,對應的奇場圖像的第n個象素和偶場圖像的第n個象素在存儲器內位置相差512%26;#215;2%26;#215;8bit,幀圖像寫入控制器通過把RTS1(奇偶場有效)信號作為寫入圖像數據的幀存儲器地址信號中的A1,把場中有效行的計數輸出信號作為幀存儲器地址信號中的A1[18:12],把行中有效象素的計數輸出信號作為幀存儲器地址信號中的A1[10:0],從而實現隔行信號變逐行信號存儲在一圖像幀存儲器中。圖4為圖像采集同步信號時序圖。當采集完一幀圖像數據時,幀圖像寫入控制器產生RDY1信號,通知乒乓開關。 在CPLD內部構造一個乒乓開關控制模塊,自動完成幀間讀寫兩個通道接口的切換。其中幀圖像寫入控制器產生的寫圖像幀的地址信號A1[18:0]、寫控制信號WR#和SAA7113的VPO[7:0]組成了圖像幀寫通道的始端接口;DSP讀圖像幀的地址線信號A2[18:0]、讀控制信號R/W#和數據線的低8位信號DI[7:0]組成了圖像幀讀通道的終端接口;RDY1、RDY2(FX0)作為幀切換就緒信號觸發通道的切換。開始采集圖像數據時,幀切換就緒信號RDY1、RDY2同時為假,圖像幀寫通道的始端接口信號與圖像幀A的接口信號RD、WE#、A[18:0]和D[7:0]連接;SAA7113的當前幀圖像數據寫入幀存儲器A;同時,圖像幀讀通道的終端接口與圖像幀B的接口信號連接,DSP從幀B中取出前一幀圖像數據進行處理;當前幀的圖像數據采集完時,幀圖像寫入控制器停止采集數據,置RDY1為真;同理,當DSP在處理完前一幀圖像時,設置引腳FXO置RDY2為真。乒乓開關模塊在檢測到RDY1、RDY2同時為真時,切換通道的接口,此時圖像幀寫通道的始端接口與圖像幀B的接口連接;SAA7113的當前幀圖像數據寫入幀存儲器B;圖像幀讀通道的終端接口與圖像幀存儲器A的接口信號連接,DSP從幀存儲器A中取出前一幀圖像數據進行處理。這樣兩幀輪換進行,實現了圖像的實時連續處理。 在DSP和SAA7113之間所有控制信號的接口邏輯和時序轉換都由CPLD來完成,增加了可靠性,簡化了PCB的版面,并且可以編程修改,提高了使用的靈活性。圖4 圖像數據采集同步信號時序圖4 S5933與DSP之間的接口設計 S5933的三種數據傳輸方式有不同的特點,應用于不同的場合。 S5933信箱方式不支持猝發(Burst)傳輸,由8個32位信箱寄存器組成,可從兩個方向進行訪問。它們平均分為兩類,分別用于PCI接口和ADD-ON接口之間的雙向信息傳輸。主機和擴展邏輯都可以通過查詢或中斷方式獲悉任一信箱寄存器的任一字節的空滿狀態,并通過相應地址訪問該字節。S5933的信箱寄存器映射在DSP的I/O空間中,從而可以實現DSP對信箱的直接操作,數據速率較低,故系統中只使用這種方式傳輸命令和狀態信息,例如PC機通知DSP設備關閉;DSP通知上層已經傳送完數據(處理完的數據的大小不是固定的)等。 S5933的FIFO方式主要由兩個接口共用的兩個32%26;#215;8比特的FIFO、讀或寫地址寄存器以及讀或寫計數器組成。兩個FIFO分別作為PCI和ADD-ON接口之間的雙向緩沖區。S5933提供了快捷方式:一組專門用于FIFO方式傳輸的控制及狀態信號,包括FIFO寄存器的直接讀、寫以及狀態信號等,用以提高數據傳輸速度,但此信號組只能工作在S5933為主控設備的情況下。S5933作為目標設備時,內部FIFO只是作為一般的寄存器,PCI總線如同訪問信箱寄存器那樣訪問它們,操作比較直觀,但不支持猝發傳輸,極大地限制了傳輸速度;S5933作為主控設備時,FIFO方式可進行DMA方式的猝發傳輸,S5933可以通過FIFO接口啟動DMA傳輸周期,傳輸過程不需要CPU的干預,傳輸的速率與外部設備的數據傳輸速率有關,可以得到很高的數據傳輸速率。S5933的DMA數據傳輸啟動方式有兩種:PCI總線接口啟動和ADD-ON總線接口啟動。啟動方式決定于由哪個接口設置讀或寫地址寄存器以及讀或寫計數器:PCI總線接口啟動方式是由PCI總線主設備(一般是PC機的客戶程序)設置DMA相關寄存器發起DMA傳輸的;ADD-ON總線接口啟動方式是由外部邏輯電路(一般是外部插卡上的CPU)設置DMA相關寄存器發起DMA傳輸的。 S5933的PASS-THRU方式使主機以內存映射方式訪問ADD-ON接口的存儲空間,只能工作在S5933是目標設備的情況下,且外部接口需要邏輯電路的支持,故不常用。

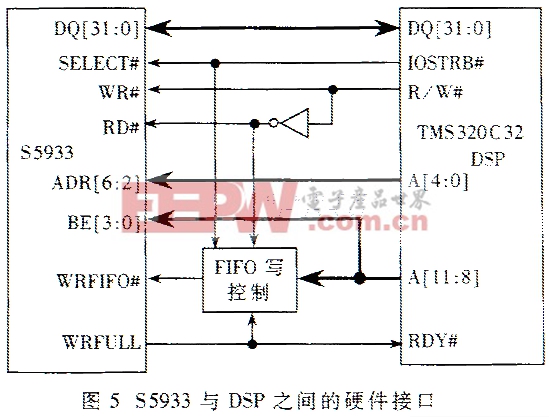

DSP與SAA7113之間的硬件接口如圖3所示,整個接口的控制邏輯,包括兩個子模塊:幀圖像寫入控制器和乒乓開關,由一塊CPLD來完成。CPLD芯片采用ALTERA公司的EPM9320RC208。兩組幀存儲器A和B采用CYPRESS公司生產的兩塊CY7C1049芯片,容量為512K%26;#215;8bit,存取時間不超過15ns,能滿足圖像實時采集要求。 SAA7113由數字視頻輸出口VPO?眼7:0,輸出視頻數據。系統設置SAA7113的輸出數據為標準的ITU 656 4?押2?押2 YUV格式,每一個象素的數據由兩個連續的字節表示。為了方便地存儲處理圖像,系統僅取一幀圖像中間的512%26;#215;512個象素作為一幀,即所取圖像幀為連續奇偶兩場圖像的中央512行,且每行取中間的512個象素的圖像塊。 利用SAA7113的同步信號,幀圖像寫入控制器模塊產生幀存儲器的地址信號、寫信號以及幀切換信號之一(RDY1)。SAA7113輸出的同步信號包括LLC、RTS0、RTS1。LLC是行鎖定系統時鐘輸出,為象素時鐘頻率的兩倍,即27MHz,用來同步數據采集,使得一個LLC周期輸出一個字節的圖像數據。在圖像數據有效時,其上升沿反相后作為幀存儲器的WE#信號。RTS0、RTS1的功能是通過編程設置SAA7113功能寄存器確定的。RTS0被設置為水平輸出參考信號(行有效信號),RTS0高電平時表示采集一行有效象素,低電平時表示場消隱信號?熏在RTSO上升沿后,幀圖像寫入控制器控制采集一行中間的512個象素數據,將其余的象素數據丟棄。RTS1被設置為垂直輸出參考信號和奇偶場信號,RTS1高電平時表示采集奇場圖像所需要的有效數據,在RTS1上升沿時,開始采集奇場圖像數據,同時它也被用來作為幀圖像開始的信號;RTS1低電平時表示采集偶場中所需要的圖像數據,在RTS1下降沿時,開始采集偶場圖像數據。在RTS1上升沿時,幀圖像寫入控制器控制采集256行象素數據作為奇場圖像;在RTS1下降沿時,順次采集下面的256行象素數據作為偶場圖像,其余的圖像行數據丟棄。使用512K%26;#215;8bit的靜態存儲器(SRAM),恰好可以存放一幀512%26;#215;512%26;#215;2%26;#215;8bit的圖像。在合成一幀圖像時,對應的奇場圖像的第n個象素和偶場圖像的第n個象素在存儲器內位置相差512%26;#215;2%26;#215;8bit,幀圖像寫入控制器通過把RTS1(奇偶場有效)信號作為寫入圖像數據的幀存儲器地址信號中的A1,把場中有效行的計數輸出信號作為幀存儲器地址信號中的A1[18:12],把行中有效象素的計數輸出信號作為幀存儲器地址信號中的A1[10:0],從而實現隔行信號變逐行信號存儲在一圖像幀存儲器中。圖4為圖像采集同步信號時序圖。當采集完一幀圖像數據時,幀圖像寫入控制器產生RDY1信號,通知乒乓開關。 在CPLD內部構造一個乒乓開關控制模塊,自動完成幀間讀寫兩個通道接口的切換。其中幀圖像寫入控制器產生的寫圖像幀的地址信號A1[18:0]、寫控制信號WR#和SAA7113的VPO[7:0]組成了圖像幀寫通道的始端接口;DSP讀圖像幀的地址線信號A2[18:0]、讀控制信號R/W#和數據線的低8位信號DI[7:0]組成了圖像幀讀通道的終端接口;RDY1、RDY2(FX0)作為幀切換就緒信號觸發通道的切換。開始采集圖像數據時,幀切換就緒信號RDY1、RDY2同時為假,圖像幀寫通道的始端接口信號與圖像幀A的接口信號RD、WE#、A[18:0]和D[7:0]連接;SAA7113的當前幀圖像數據寫入幀存儲器A;同時,圖像幀讀通道的終端接口與圖像幀B的接口信號連接,DSP從幀B中取出前一幀圖像數據進行處理;當前幀的圖像數據采集完時,幀圖像寫入控制器停止采集數據,置RDY1為真;同理,當DSP在處理完前一幀圖像時,設置引腳FXO置RDY2為真。乒乓開關模塊在檢測到RDY1、RDY2同時為真時,切換通道的接口,此時圖像幀寫通道的始端接口與圖像幀B的接口連接;SAA7113的當前幀圖像數據寫入幀存儲器B;圖像幀讀通道的終端接口與圖像幀存儲器A的接口信號連接,DSP從幀存儲器A中取出前一幀圖像數據進行處理。這樣兩幀輪換進行,實現了圖像的實時連續處理。 在DSP和SAA7113之間所有控制信號的接口邏輯和時序轉換都由CPLD來完成,增加了可靠性,簡化了PCB的版面,并且可以編程修改,提高了使用的靈活性。圖4 圖像數據采集同步信號時序圖4 S5933與DSP之間的接口設計 S5933的三種數據傳輸方式有不同的特點,應用于不同的場合。 S5933信箱方式不支持猝發(Burst)傳輸,由8個32位信箱寄存器組成,可從兩個方向進行訪問。它們平均分為兩類,分別用于PCI接口和ADD-ON接口之間的雙向信息傳輸。主機和擴展邏輯都可以通過查詢或中斷方式獲悉任一信箱寄存器的任一字節的空滿狀態,并通過相應地址訪問該字節。S5933的信箱寄存器映射在DSP的I/O空間中,從而可以實現DSP對信箱的直接操作,數據速率較低,故系統中只使用這種方式傳輸命令和狀態信息,例如PC機通知DSP設備關閉;DSP通知上層已經傳送完數據(處理完的數據的大小不是固定的)等。 S5933的FIFO方式主要由兩個接口共用的兩個32%26;#215;8比特的FIFO、讀或寫地址寄存器以及讀或寫計數器組成。兩個FIFO分別作為PCI和ADD-ON接口之間的雙向緩沖區。S5933提供了快捷方式:一組專門用于FIFO方式傳輸的控制及狀態信號,包括FIFO寄存器的直接讀、寫以及狀態信號等,用以提高數據傳輸速度,但此信號組只能工作在S5933為主控設備的情況下。S5933作為目標設備時,內部FIFO只是作為一般的寄存器,PCI總線如同訪問信箱寄存器那樣訪問它們,操作比較直觀,但不支持猝發傳輸,極大地限制了傳輸速度;S5933作為主控設備時,FIFO方式可進行DMA方式的猝發傳輸,S5933可以通過FIFO接口啟動DMA傳輸周期,傳輸過程不需要CPU的干預,傳輸的速率與外部設備的數據傳輸速率有關,可以得到很高的數據傳輸速率。S5933的DMA數據傳輸啟動方式有兩種:PCI總線接口啟動和ADD-ON總線接口啟動。啟動方式決定于由哪個接口設置讀或寫地址寄存器以及讀或寫計數器:PCI總線接口啟動方式是由PCI總線主設備(一般是PC機的客戶程序)設置DMA相關寄存器發起DMA傳輸的;ADD-ON總線接口啟動方式是由外部邏輯電路(一般是外部插卡上的CPU)設置DMA相關寄存器發起DMA傳輸的。 S5933的PASS-THRU方式使主機以內存映射方式訪問ADD-ON接口的存儲空間,只能工作在S5933是目標設備的情況下,且外部接口需要邏輯電路的支持,故不常用。 本系統是圖像處理的一個實驗平臺,既要求數據傳輸率高,又要求有一定的升級功能和靈活性。因此,系統采用FIFO數據傳輸方式。當采集的圖像數據量大且要求傳輸速度高時,可以采用FIFO方式中的PCI總線接口啟動DMA方式,使用DMA傳輸;有一些應用場合,要傳送的數據個數不明確,例如圖像壓縮后的數據量是不一定的,可以使用外加總線接口啟動DMA的傳輸方式傳送壓縮圖像,而用信箱方式傳送命令和圖像狀態信息。在這種方式下,S5933的外加總線操作寄存器全部映射在TMS320C32 DSP的選通控制信號IOSTRB#控制的空間中,使DSP對PCI接口傳輸的數據的控制十分簡單,就象操作自身的外圍接口一樣。S5933與DSP之間的硬件接口的具體連接方式如圖5所示。 S5933和DSP之間的硬件連接,就是利用DSP的讀寫信號R/W#、地址選通控制信號IOSTRB#、外部設備就緒信號RDY#和部分地址信號以及S5933的FIFO狀態信號WRFULL進行簡單的時序和邏輯組合,生成對S5933的外加總線接口的讀寫控制信號:WR#、RD#、SELECT#、ADR[6:2]、BE[3:0]、WRFIFO#。S5933的數據總線與DSP的數據總線相連接,數據線寬度為32位,以便提供盡可能高的傳輸速率。 本文采用PCI接口芯片S5933、DSP芯片TMS320C32和視頻輸入處理芯片SAA7113設計實現的視頻圖像處理實驗平臺系統可以實現圖像的高速連續采集,進行圖像壓縮、圖像處理等算法的驗證,達到了系統設計的目標。本系統具有使用靈活、升級方便等特點。考慮到DSP芯片的內部RAM有限,程序不能完全在片內運行,在進行一些復雜的圖像處理運算時,速度會受到限制,故本系統僅適用于靜態圖像的處理算法研究。

本系統是圖像處理的一個實驗平臺,既要求數據傳輸率高,又要求有一定的升級功能和靈活性。因此,系統采用FIFO數據傳輸方式。當采集的圖像數據量大且要求傳輸速度高時,可以采用FIFO方式中的PCI總線接口啟動DMA方式,使用DMA傳輸;有一些應用場合,要傳送的數據個數不明確,例如圖像壓縮后的數據量是不一定的,可以使用外加總線接口啟動DMA的傳輸方式傳送壓縮圖像,而用信箱方式傳送命令和圖像狀態信息。在這種方式下,S5933的外加總線操作寄存器全部映射在TMS320C32 DSP的選通控制信號IOSTRB#控制的空間中,使DSP對PCI接口傳輸的數據的控制十分簡單,就象操作自身的外圍接口一樣。S5933與DSP之間的硬件接口的具體連接方式如圖5所示。 S5933和DSP之間的硬件連接,就是利用DSP的讀寫信號R/W#、地址選通控制信號IOSTRB#、外部設備就緒信號RDY#和部分地址信號以及S5933的FIFO狀態信號WRFULL進行簡單的時序和邏輯組合,生成對S5933的外加總線接口的讀寫控制信號:WR#、RD#、SELECT#、ADR[6:2]、BE[3:0]、WRFIFO#。S5933的數據總線與DSP的數據總線相連接,數據線寬度為32位,以便提供盡可能高的傳輸速率。 本文采用PCI接口芯片S5933、DSP芯片TMS320C32和視頻輸入處理芯片SAA7113設計實現的視頻圖像處理實驗平臺系統可以實現圖像的高速連續采集,進行圖像壓縮、圖像處理等算法的驗證,達到了系統設計的目標。本系統具有使用靈活、升級方便等特點。考慮到DSP芯片的內部RAM有限,程序不能完全在片內運行,在進行一些復雜的圖像處理運算時,速度會受到限制,故本系統僅適用于靜態圖像的處理算法研究。

評論