基于開關電容共模反饋理論分析

1引言

全差分開關電容電路由于具有全差分電路的高輸出擺幅和對電源等共模噪聲的抑制以及開關電容電路的高精度而成為常用電路形式[1,2,3,4,8]。而全差分電路設計的關鍵和難點是共模反饋電路的設計[2]。缺乏好的共模反饋電路會造成輸出共模電壓波動,并會通過電路的不對稱性而轉化為差分輸出,破壞差分輸出信號。另一方面,輸出共模偏離預定值會導致差分輸出擺幅受限,進而造成削頂或削底失真,此時檢測出的共模值偏離實際輸出錯誤的共模值,進而返回錯誤的控制電壓進一步造成共模電壓偏離正常值,嚴重影響電路性能。

直到最近一直有各種論文在對開關電容共模反饋電路進行分析[3,4,5,6],但是各種分析仍然不能對開關電容共模反饋進行全面的系統的理論分析,并存在各種缺陷。由于和連續時間共模反饋電路的工作機理有些不同,并且處于采樣系統中,很難用連續域的手段進行分析和仿真,所以長期以來缺乏足夠的分析和設計的依據,致使設計帶有一定的盲目性。

本文總結并提出了新的開關電容共模反饋的連續時間等效共模和差模分析模型,對開關電容共模反饋電路的共模(共模穩定性和環路建立時間)和差模特性進行分析,進而為開關電容共模反饋電路設計提供了強有力的理論支持。

2開關電容共模反饋電路的理論分析

2.1 開關電容共模反饋電路的基本原理和結構

共模反饋電路一般分為兩個部分:共模檢測電路和比較放大器電路。基本原理是通過共模檢測電路檢測出輸出共模電壓,然后輸入比較放大器電路和預先指定的輸出共模參考電壓相比較,將它們的差值放大并返回到原電路對輸出共模電壓的偏移進行校正[2]。共模反饋電路可以分為連續時間共模反饋電路和開關電容共模反饋電路。連續時間共模反饋電路主要應用于連續時間電路中,但是具有限制差模輸出信號擺幅,增加差模負載,增加靜態功耗和檢測共模電壓非線性等缺點。開關電容共模反饋電路在這幾方面具有優勢,但因為會引入時鐘耦合和離散工作狀態使差分輸出信號出現毛刺而不適合用于連續時間電路中。開關電容共模反饋電路已經成功應用于數據采樣系統中,尤其是在全差分開關電容電路中。

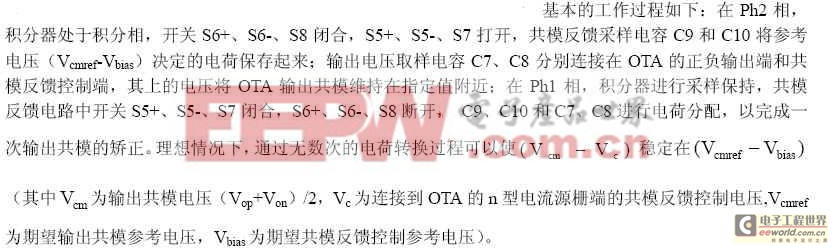

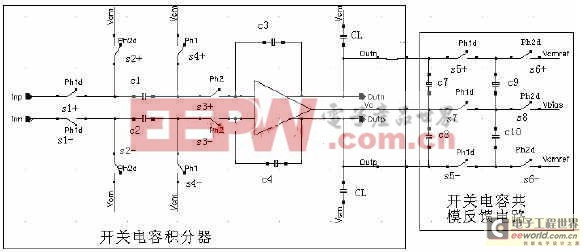

連續時間共模反饋電路對輸出共模電壓偏移的校準是連續進行的。但開關電容共模反饋電路對輸出共模電壓的反饋控制是離散的,是在每次電荷轉移的半個時鐘周期中完成的,校準也是在不斷重復的半時鐘周期內完成的。所以分析方法和連續時間共模反饋電路不同。在論文[6]中給出了開關電容共模反饋的電路,一直沿用至今。一個帶開關電容共模反饋電路的開關電容積分器如圖1所示。左半電路為開關電容積分器電路,右半電路為開關電容共模反饋電路。其中的OTA如圖2所示。

圖1 帶開關電容共模反饋的開關電容積分器

圖2 開關電容電路中的放大器原型

2.2 開關電容共模反饋電路的共模分析

開關電容共模反饋的作用機制和其他共模反饋的作用機制不盡相同。從本質上說,開關電容共模反饋控制的是通過每次電荷轉移讓 穩定在 ,而非像其他連續時間共模反饋那樣直接檢測和控制輸出共模電壓。因此,實際上開關電容共模反饋的Vcm最終無法保證能穩定在指定電壓Vcmref,只能在一定范圍內預估。

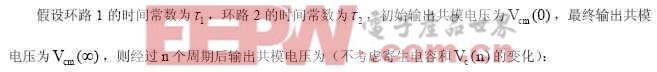

假設分析的電路完全對稱,則電路的共模環路和差模環路在穩定工作狀態下不會相互干擾。由于開關電容共模反饋電路存在兩個離散狀態,因此無法用和連續時間共模反饋相同的方法進行共模等效分析。在傳統的分析中,按照和連續時間共模反饋相同的共模等效方法和評價指標(共模反饋環路單位增益帶寬、環路增益和相位裕度)來近似分析開關電容共模反饋電路。然而這些指標在開關電容共模反饋電路中有著不同的意義。

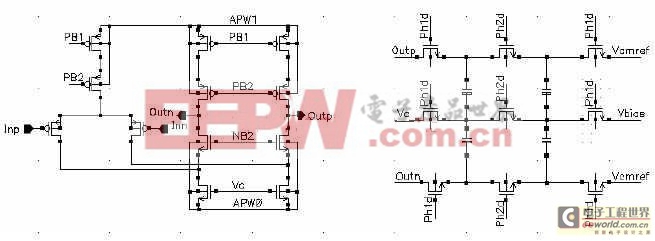

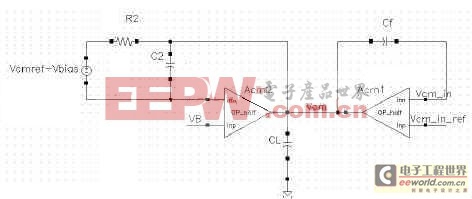

圖3 開關電容電路的共模分析等效模型

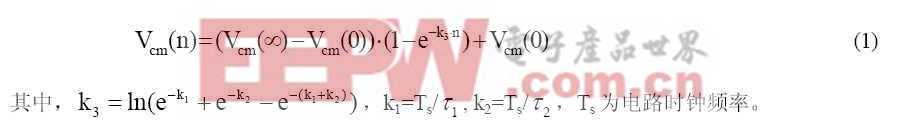

本文提出一種新的開關電容共模反饋的共模等效模型,如圖3所示。在圖3的等效電路中有2個共模放大器Acm1和Acm2,Acm1是由主放大器共模共模通路組成,Acm2是由共模反饋通路組成。其中Acm2周圍存在兩個環路,分別存在各自的建立過程。環路1由R2和C2組成。環路2由Acm2和C2組成。其中 ,C1即圖1中C9和C10,C2即圖1中的C7和C8,Cf為積分器積分電容,Ts為采樣時鐘周期。存在兩種情況,對應不同的結論:(1)在環路2帶寬遠大于環路1帶寬的情況下,每次電荷轉移完全。此時稱為環路1速度受限。在此條件下,環路1的建立過程決定了共模穩定的時間。其建立時間常數 。如果C1=C2,則 ,通常需要5個周期以上才能從一次輸出共模變動中恢復過來。對于經常出現的周期接近Ts的共模波動,開關電容共模反饋電路幾乎沒有任何穩定作用。而通過增加開關電容共模反饋采樣電容來提高輸出共模電壓穩定速度的做法不可行,此電容過大不僅會極大地增加差模環路的負載,還會造成巨大的差模毛刺。可見在此情況下,對開關電容共模反饋電路而言,無論電路工作在什么采樣頻率下,其輸出共模電壓達到一定精度所需的時鐘周期數是不變的,而連續時間共模反饋電路對輸出共模電壓穩定的速度和電路工作的采樣頻率無關。一個100MHz單位增益帶寬的連續時間共模反饋電路對應的時間常數為10ns。和連續時間共模反饋電路增加共模環路單位增益帶寬來減小輸出共模電壓穩定時間不同的是,在此情況下,開關電容共模反饋電路中增加共模環路(Acm2和C2組成的環路)帶寬并不能減小輸出共模電壓的穩定時間,而只能減小每次電荷轉移的時間,或建立精度。(2)在環路1帶寬遠大于環路2帶寬的情況下,每次電荷傳遞不完全,輸出共模電壓穩定時間較長,輸出共模電壓不穩。此時稱為環路2速度受限。仍然假設環2的環路單位增益頻率為100MHz,C1=C2,時鐘頻率為Ts,當100M5/Ts(假設5 將電荷傳遞完畢),即Ts50ns,或電路工作頻率高于20MHz時,開關電容共模反饋電路不能在每次C1、C2電荷傳遞過程中完整地傳遞電荷,因此也會出現輸出共模電壓穩定速度下降的問題。

因此,開關電容共模反饋實際上是由兩個環路建立時間共同決定的。低速工作時(10MHz以下),連續時間共模反饋電路的穩定速度會高于開關電容共模反饋電路。此時,開關電容共模反饋電路環1比環2的穩定速度慢,因此穩定速度決定于環1。所以連續時間共模反饋電路的穩定速度會快于開關電容共模反饋電路的穩定速度。當高速工作時(100MHz以上),開關電容共模反饋電路速度受限于環2,此環的建立速度和連續時間共模反饋時間相當,但由于存在兩個環路和兩個建立過程,總的來說,會比連續時間共模反饋電路建立速度慢。所以在共模穩定速度方面,連續時間共模反饋電路會更優秀,尤其是在低頻電路中。

由此得到開關電容共模反饋和連續時間共模反饋的等效模型,因此可以借用連續時間共模反饋理論對開關電容共模反饋電路進行分析。可以看出k3k1,k2,也證明在連續時間共模反饋電路環路單位增益頻率等于開關電容環路2的單位增益頻率條件下,開關電容共模反饋的建立速度會小于連續時間共模反饋電路。

假設兩環的環路時間常數相等,均為Ts(采樣周期),與其對應的連續時間共模反饋環路時間常數也為Ts,此時開關電容

電荷放大器相關文章:電荷放大器原理 電容相關文章:電容原理 電子負載相關文章:電子負載原理 絕對值編碼器相關文章:絕對值編碼器原理

評論