由開關電源驅動的高速ADC設計

本文引用地址:http://www.j9360.com/article/228094.htm

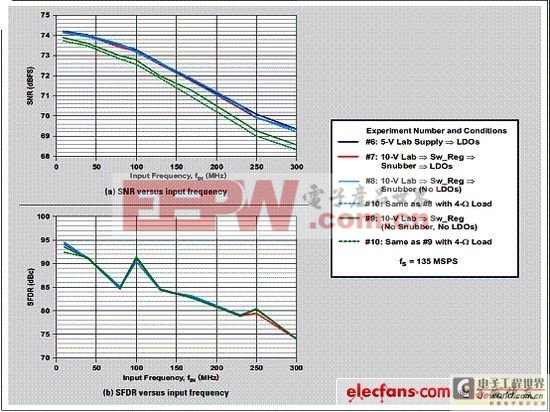

本文引用地址:http://www.j9360.com/article/228094.htm圖12:10到300MHz的輸入頻率掃描。

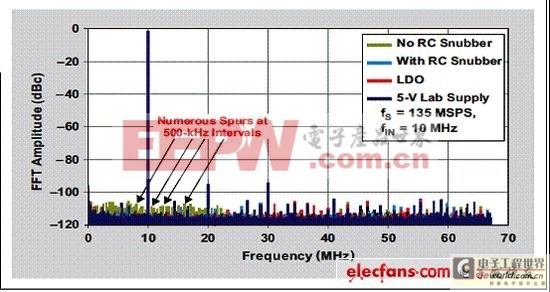

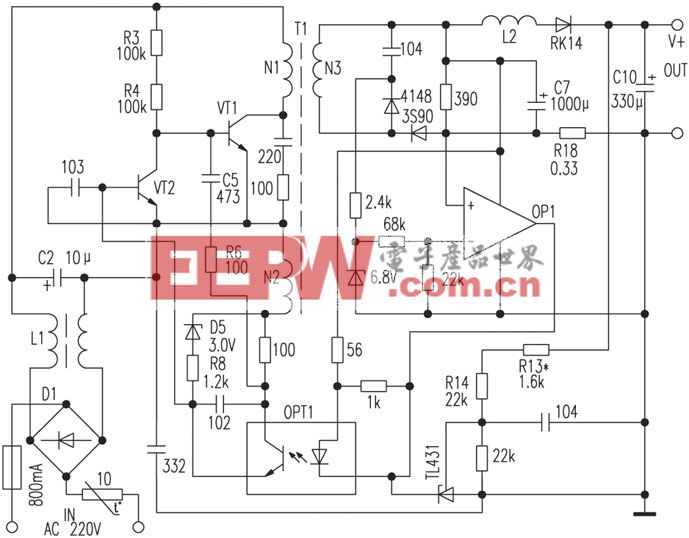

比較圖13所示FFT圖,我們知道無RC緩衝器SNR稍微減少的塬因。去除RC緩衝器電路后,在ADS6148輸出能譜中,我們可看到分佈間隔約為500kHz(TPS5420開關頻率)的眾多小突波,如圖13所示。相較于ADS5483,這些小突波更具主導性,并且因為ADS6148的固有低PSRR SNR大幅降低。但是,圖13所示FFT圖還顯示添加的RC緩衝器電路較好地彌補了這一不足。

圖13:大批突波的65k點FFT圖。

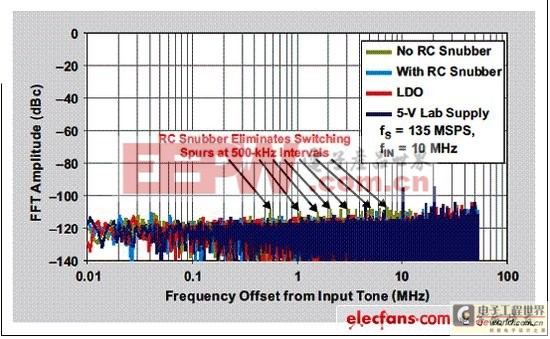

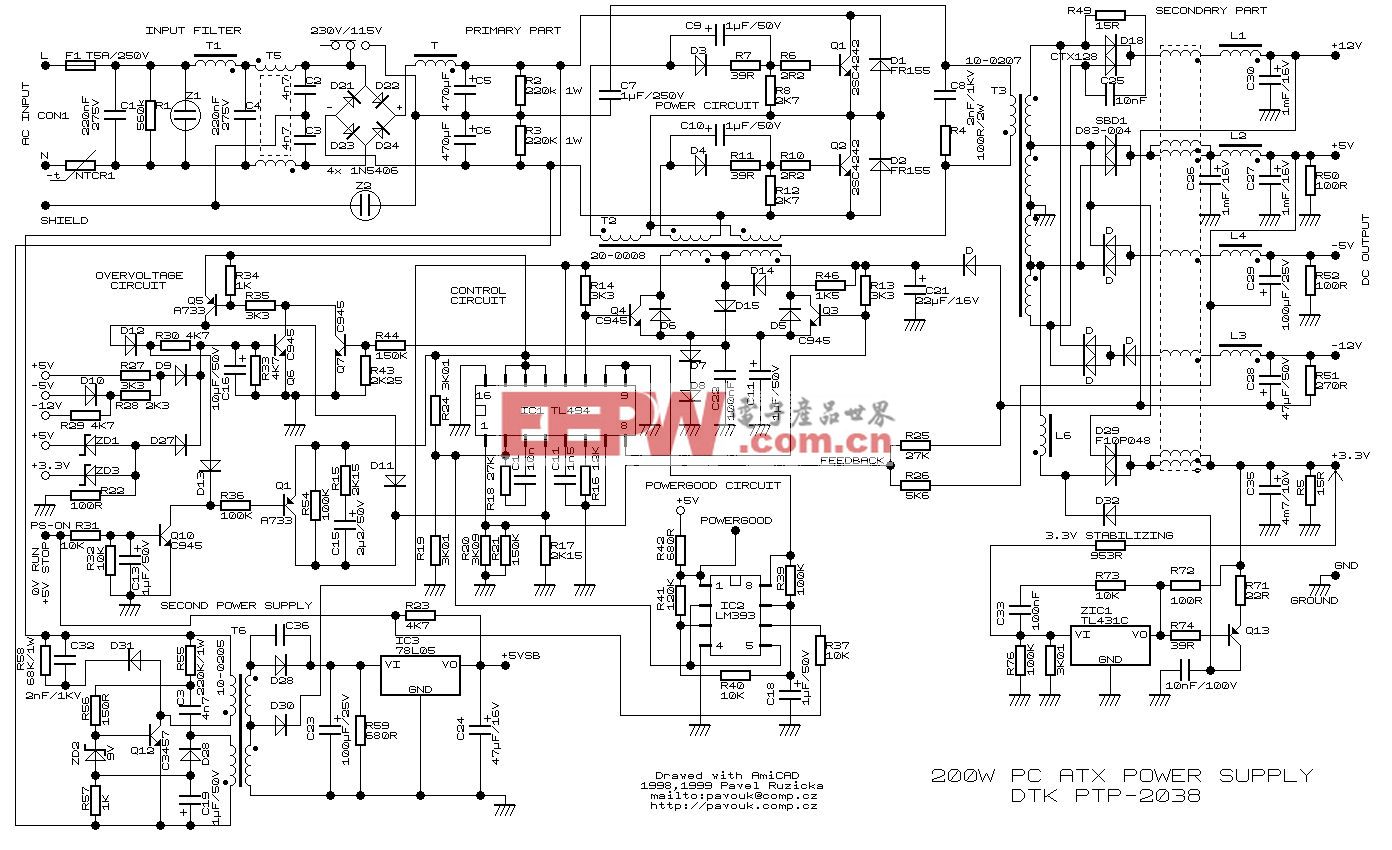

圖14所示標準化FFT圖顯示交換式穩壓器的突波高出ADC平均雜訊層約5到6dB。其非常低,以至于其對SFDR減少無法產生影響,但卻明顯地影響了ADC的SNR。

圖14:標準化FFT圖顯示使用RC緩衝器的好處。

評論