由開關(guān)電源驅(qū)動(dòng)的高速ADC設(shè)計(jì)

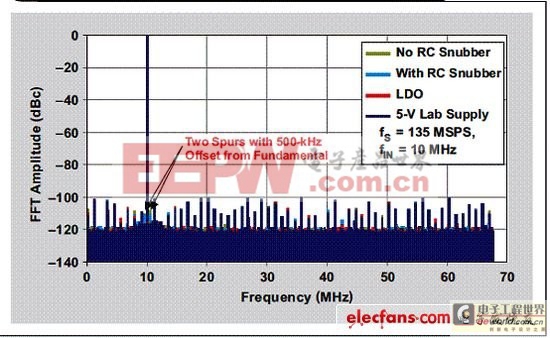

圖6:500kHz偏置突波65k點(diǎn)FFT圖。

RC緩沖器

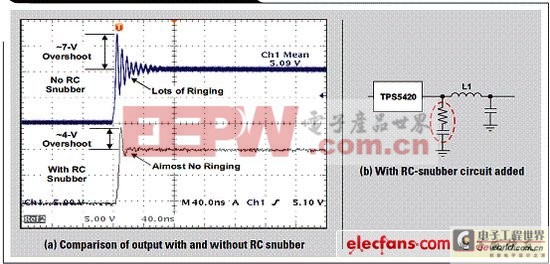

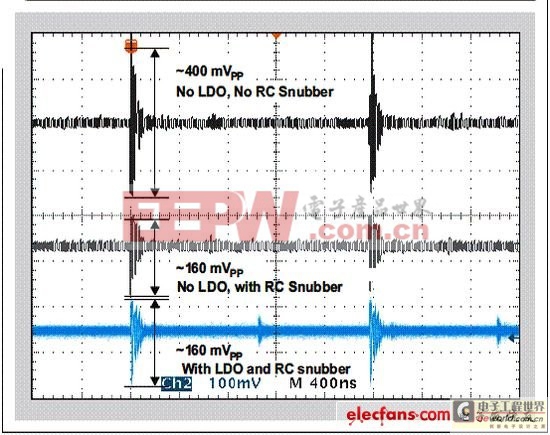

降壓穩(wěn)壓器輸出能夠以相當(dāng)高的開關(guān)速度對(duì)非常大的電壓實(shí)施開關(guān)作業(yè)。本文中,將TPS5420的輸入電壓軌設(shè)定為10V,我們可在輸出端觀測到許多過衝和振鈴,如圖7a所示。為了吸收一些電源電路電抗能量,我們將RC緩衝電路添加到了TPS5420的輸出(請參見圖7b)。該電路提供了一個(gè)高頻接地通路,其對(duì)過衝起到了一些阻滯作用。圖7a顯示RC緩衝器降低過衝約50%,并且?guī)缀跬耆苏疋彙N疫x用了R=2.2Ω和C=470pF的元件值。穩(wěn)壓器的開關(guān)頻率範(fàn)圍可以為500kHz到約6MHz,具體取決于製造廠商,因此可能需要我們對(duì)R和C值進(jìn)行調(diào)節(jié)。這種解決方案的代價(jià)是帶來一些額外的分流電阻AC功耗(儘管電阻非常小),其降低穩(wěn)壓器總功效不足1%。

圖7:TPS5420交換式穩(wěn)壓器。

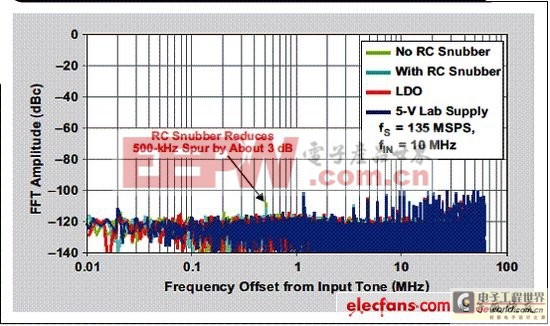

我們將10MHz輸入訊號(hào)標(biāo)準(zhǔn)化FFT圖繪製出來,以對(duì)比‘實(shí)驗(yàn)1’到‘實(shí)驗(yàn)4’(請參見圖8)。TPS5420的突波在約500kHz偏置時(shí)清晰可見。緩衝器降低突波振幅約3dB,而低雜訊LDO則完全消除了突波。需要注意的是,RC緩衝器(無LDO)的突波振幅約為-112dBc,遠(yuǎn)低于ADS5483平均突波振幅,因此SFDR性能并未降低。

圖8:‘實(shí)驗(yàn)1’到‘實(shí)驗(yàn)4’的標(biāo)準(zhǔn)FFT圖。

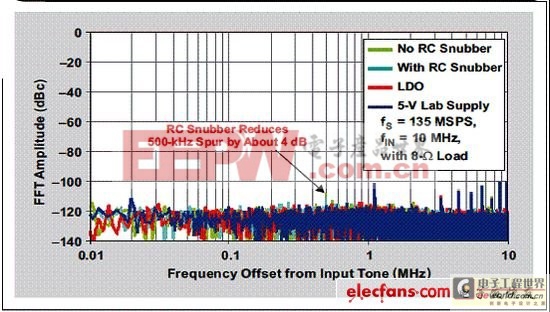

在‘實(shí)驗(yàn) 5‘中,我們將一個(gè)8Ω功率電阻添加到5-VVDDA電壓軌,旨在模擬電源的重負(fù)載。標(biāo)準(zhǔn)化FFT圖(請參見圖9)并未顯示出很多不同。去除RC緩衝器以后,突波增加約4.5dB;其仍然遠(yuǎn)低于平均突波振幅。

圖9:添加 8Ω負(fù)載的標(biāo)準(zhǔn)化FFT圖。 采用CMOS技術(shù)的ADC

當(dāng)關(guān)注如何在保持較佳的SNR和SFDR性能的同時(shí)也盡可能地降低功耗時(shí),我們一般利用CMOS技術(shù)來開發(fā)高速資料轉(zhuǎn)換器。但是,CMOS轉(zhuǎn)換器的PSRR一般并不如BiCOM ADC的好。ADS6148產(chǎn)品說明書列出了25dB的PSRR,而在類比輸入電源軌上ADS5483的PSRR則為60dB。

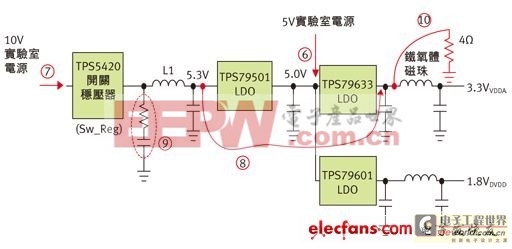

ADS6148EVM使用一種板上電源,其由一個(gè)交換式穩(wěn)壓器(TPS5420)和一個(gè)低雜訊、5V輸出LDO(TPS79501)組成,后面是一些3.3V和1.8V電源軌的低雜訊LDO(請參見圖10)。與使用ADS5483EVM的5個(gè)實(shí)驗(yàn)類似,我們使用ADS6148EVM進(jìn)行了下面另外5個(gè)實(shí)驗(yàn),其注意力只集中在3.3VVDDA電壓軌的雜訊上面。1.8VDVDD電壓軌外置TPS5420實(shí)驗(yàn)顯示對(duì)SNR和SFDR性能沒有什么大的影響。

圖10:使用ADS6148EVM的5個(gè)實(shí)驗(yàn)電源結(jié)構(gòu)。

實(shí)驗(yàn)6

將一個(gè)5V實(shí)驗(yàn)室電源連接到兩個(gè)低雜訊LDO(一個(gè)使用3.3V輸出,另一個(gè)使用1.8V輸出)的輸入。LDO并未對(duì)實(shí)驗(yàn)室電源帶來任何有影響的雜訊。

實(shí)驗(yàn)7

將一個(gè)10V實(shí)驗(yàn)室電源連接到TPS5420降壓穩(wěn)壓器,其與一個(gè)5.3V輸出連接,像‘實(shí)驗(yàn)2’連接ADS5483一樣。TPS79501產(chǎn)生了一個(gè)過濾后的5.0V電壓軌,對(duì)于3.3V輸出和1.8V輸出LDO提供輸入,如圖10所示。

實(shí)驗(yàn)8

所有3.3VVDDA電壓軌LDO均被加以旁路。TPS5420配置為一個(gè)3.3V輸出,該輸出直接連接到3.3VVDDA電壓軌。TPS79601產(chǎn)生1.8VDVDD電壓軌,并透過一個(gè)外部5V實(shí)驗(yàn)室電源供電。

實(shí)驗(yàn)9

該實(shí)驗(yàn)配置方法與‘實(shí)驗(yàn)8’相同,但去除了TPS5420輸出的RC緩衝器電路。

實(shí)驗(yàn)10

一個(gè)4Ω功率電阻連接到TPS5420的3.3V輸出。這樣做可大幅增加TPS5420的輸出電流,因而類比一個(gè)附加負(fù)載。另外,像‘實(shí)驗(yàn)5’的ADS5483一樣,它帶來了更高的開關(guān)突波和更多的振鈴。

圖11顯示了‘實(shí)驗(yàn)7’、‘實(shí)驗(yàn)8’和‘實(shí)驗(yàn)9’產(chǎn)生的一些3.3VVDDA 輸出波形。有或無LDO的峰值電壓振幅存在一些差異,但RC緩衝器可降低60%的峰值雜訊。

圖11:鐵氧體磁珠后測得3.3VVDDA 電壓軌實(shí)驗(yàn)示波器截圖對(duì)比。

測量結(jié)果

利用輸入訊號(hào)頻率掃描,透過比較‘實(shí)驗(yàn)6’到‘實(shí)驗(yàn)10’,我們可以研究ADS6148對(duì)電源雜訊的感應(yīng)性。先使用135MSPS然后使用210MSPS的採樣速率(fs)對(duì)叁個(gè)ADS6148EVM進(jìn)行數(shù)次實(shí)驗(yàn)。我們并未探測到較大的性能差異。

使用135MSPS採樣速率,SNR和SFDR的頻率掃描如圖12所示。高達(dá)300MHz輸入頻率下SNR的最大變化為0.1到0.2dB。但是,一旦移除了RC緩衝器電路,雜訊便極大增加,因而降低SNR約0.5到1dB。

圖12b顯示了5次ADS6148實(shí)驗(yàn)輸入頻率的SFDR變化。我們并未觀測到較大的性能降低。

評(píng)論