對FIR數字濾波器的FPGA實現的研究

3 實例設計與仿真

3.1 FIR濾波器的設計

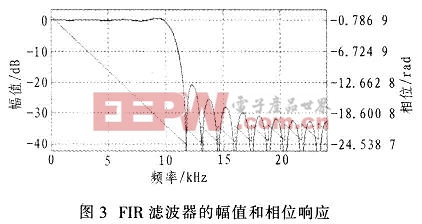

利用Matlab中的FDATool工具設計一個33階,Fs=48kHz,Fc=10.8 kHz的FIR濾波器,其幅值、相位響應見圖3。為了便于FIR濾波器的FPGA實現,減小誤差,將濾波器的系數量化取整后,在FPGA中實現采用的濾波系數為{-11,14,18,-11,-25,4,32,6,-38,-21,43,45,-47,-96,50,319,457,319,50,-96,-47,45,43,-21,-38,6,32,4,-25,-11,18,14,-11}。

3.2 FIR濾波器的FPGA實現與仿真

在Xilinx 10.1 ISE平臺中,選用Virtex-5系列的XC5VSXT50T器件,用Verilog HDL語言設計串行結構、并行結構的、以及DA結構,并在ModelSim中對3種結構實現進行仿真。設計中輸入數據的位寬設為16位,而輸入數據在運算處理前位寬擴展到17位。所用仿真激勵為單位階躍響應,時鐘周期為Tck=10 ns。ModelSim中的仿真結果如圖4所示。

圖4中依次為改進的串行實現,并行實現和DA實現的仿真結果,其濾波周期分別為180 ns,10 ns和180 ns。上述設計的改進串行結構、并行結構和DA結構分別在XC5VSX50T中實現后,所消耗的FPGA內部各種資源如表1所示。

從表l可以看出,并行實現消耗的資源最多,其次是DA實現,最小是串行實現。而從濾波速度上來看,并行濾波速度最快,1個時鐘周期便可濾波1次;而串行實現速度慢,其濾波周期取決于濾波器的階數,對17階的對稱濾波器而言,濾波一次占9個時鐘周期,濾波輸出占1個時鐘周期;相對串行實現和并行實現,DA實現的濾波周期取決于處理的數據寬度,上述設計中DA實現的濾波處理數據位寬是17位,所以濾波一次占17個時鐘周期,濾波輸出占用1個時鐘周期。

4 結束語

在實際應用中,當濾波器設計對濾波速度要求不高時,可采用串行結構或改進串行結構來實現,這樣可以選取資源較少的器件,降低設計成本;當對濾波速度有較高要求時,可以考慮采用并行或DA來實現。并行實現濾波周期為時鐘周期,速度快,但消耗的資源多,成本高;DA實現速度較快,消耗的資源較少,成本耗費較低。在數字多普勒接收機的實現過程中,根據接收機的性能要求以及所選用的FPGA器件資源,選取最優的FlR濾波器實現結構。隨著FPGA查找技術的發展,具有較快的濾波速度和消耗較少資源的DA算法在FIR數字濾波領域得到了廣泛應用。

評論