對FIR數字濾波器的FPGA實現的研究

2 基于分布式算法的FIR濾波器的實現

2.1 分布式算法原理

上世紀70年代Croisie提出了分布式算法DA(Distributed Arithmetic),但由于其特別適合用FPGA實現,所以直到Xilinx公司在FPGA中使用查找表(LUT)后,DA才被廣泛應用在FPGA求乘積和中。

FIR的濾波輸出y可以表示為輸入x和系數h的內積:

由上述推導可知,分布式算法是一種以實現乘加運算為目的的運算方法。它與傳統實現乘加運算的先后順序不同。分布式算法在完成乘加功能時,是通過將各輸入數據每一對應位產生的部分積預先進行相加形成相應部分積,然后在對各部分積預先進行累加形成最終結果;而傳統算法是等到所有乘積產生之后再進行相加來完成乘加運算。

2.2 分布式FIR的實現結構

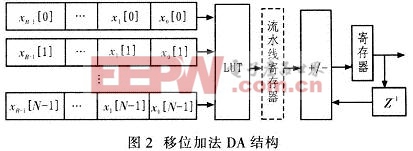

圖2為分布式FIR濾波器的直接實現結構。對于小位寬的數據,DA算法不僅速度快,而且所占用的芯片資源少。

2.3 性能優化方法

1)流水線結構法 在濾波器中間增加適當的寄存器,構成流水線結構。在并行結構實現中添加流水線結構,可以提高濾波器速度,使其工作在更高的工作頻率。對于速度固定的數據,可以通過多次復用乘累加器來節省資源。

2)查找表分隔法 在用LUT實現分布式算法時,由于LUT的規模隨著N的增加呈現指數增長,如果濾波器系數N過大,則查找表的規模十分龐大。為了減小規模,可以利用部分表計算。由于FIR濾波器是線性濾波器,因此低階濾波器輸出可以相加,由此定義一個高階濾波器的輸出。例如,把16輸入的查找表分割成4個并行的查找表。

查找表的分隔技術和流水線技術可以大大減小設計規模,同時并不會降低濾波速度。使用DA算法實現的FlR濾波器與傳統的算法相比,DA算法可以極大地減少硬件電路規模,很容易實現流水線處理,提高電路的執行速度。

2.4 3種結構實現的比較

改進串行結構、并行結構、DA結構實現的比較如下:

1)改進串行結構 ①優點:使用資源少,只需一些寄存器、乘累加器便可完成整個濾波運算;②缺點:濾波速度慢,一次濾波所需的時鐘數由濾波器的階數決定。階數較高的濾波器,濾波周期很大,無法實現高速濾波。

2)并行結構 ①優點:完成濾波的速度快,直接并行濾波器可以在一個時鐘周期內完成一次濾波;②缺點:消耗大量的乘累加器,器件延遲較大,工作頻率不可能太高。

3)DA結構 與串行結構實現相比,DA實現濾波速度較快,其濾波周期由數據寬度決定而與濾波器的階數無關;而與并行實現相比,DA實現消耗的資源較少。且容易實現流水線處理,提高電路的執行速度。

在設計中,當資源成本為主要制約時,根據速度要求,選擇串行結構實現或DA結構實現;而當速度成為主要制約時,則根據資源成本因素,選擇并行實現結構或DA結構實現。在一般的應用設計中,一般采用DA結構實現。

評論