基于ARM的嵌入式RIFD讀寫器設計

引言

RFID 利用了電磁波空間耦合、傳播進行通信,以達到自動識別被標識對象,獲取對象信息的目的。同其他一些識別技術相比,射頻識別技術具有高效快捷、非接觸、無污染、識別率高等突出優點。識別過程無需人工干預,可在惡劣環境下工作,能夠應用到很多行業。

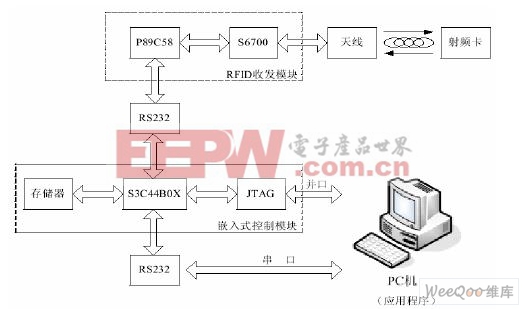

1.RIFD 讀寫器的硬件總體設計

圖 1 讀寫器的硬件總體設計

RFID 系統主要由射頻卡、讀寫器以及計算機系統組成。系統的工作原理如下:讀寫器通過天線發送出 13.56MHz 的射頻信號,當射頻卡進入讀寫器工作場時,天線產生感應電流,從而射頻卡獲得能量被激活并向讀寫器發送出自身編碼等信息,讀寫器接收到來自射頻卡的載波信號,對接收的信號進行解調和解碼后發送至 PC 機進行處理,PC 機根據邏輯運算判斷該射頻卡的合法性,針對不同的設定做出相應的處理和控制,發出指令信號,射頻卡的數據解調部分從接收到的射頻脈沖中解調出數據并送到控制邏輯,控制邏輯接受指令完成存儲、發送數據或其他操作。

2. 硬件選型

在整個系統中,RFID 收發模塊的功能是當接收到來自射頻卡的載波信號時,對該信號進行解調和解碼,并且將信息進行編碼和調制后發送到射頻卡中,要實現上述功能就需要一款內部封裝有發送調制器和接收調制器的射頻芯片,選用了射頻芯片 S6700。S6700 芯片的時序是通過控制產生的,因此選用了單片機P89C58,利用它的 I/O 口進行控制。因為系統中使用的射頻卡是疏耦合 IC卡,所以它與 S6700 芯片之間的協議標準采用了 ISO 15693,C 語言進行編程。

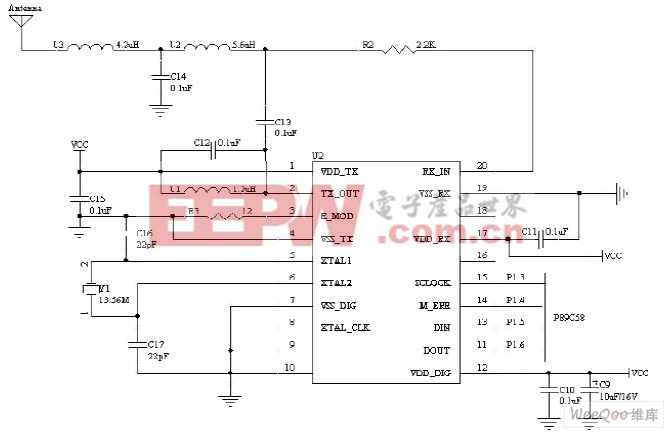

3.RFID 收發模塊硬件電路設計

RFID 收發模塊的主芯片是 TI 公司的射頻芯片 S6700,該芯片的通信接口主要使用三條線:SCLOCK、DIN 和 DOUT。除了通信線外,還有一條 M_ERR 線,用來表征通信是否正常;應用電路如圖2 所示:

圖 2 RFID 收發模塊硬件電路

S6700 的 SCLOCK、DIN、DOUT 分別由 P89C58 的 P1.3、P1.5 和 P1.6 進行控制,由于單片機 P89C52 應用比較廣泛。R2 為調制深度選擇電阻,當 R2 為 12 歐姆時,調制深度為 10%;當 R2 為 18 歐姆時,調制深度為 20%。SCLOCK 為雙向時鐘線,分別由單片機 P89C58 和 S6700芯片在不同的情況下進行控制:發送數據時由 P89C58 控制,接收數據時由 S6700 控制。在收發數據時,每個數據位在 SCLOCK 的上升沿被鎖存,當 SCLOCK 為高時,數據位必須固定且保持不變,只有當 SCLOCK 為低時,傳送的數據才能被改變;DIN 為數據輸入線,S6700 芯片通過該線接收來自 P89C58 的命令和數據;DOUT 為數據輸出線,S6700 芯片通過該線將回應數據發送給P89C58,同時該線還可用于監測S6700 芯片內部數據緩沖區的情況。M_ERR 線用來表征在同時讀多張卡時數據的沖突情況。該線由于內部下拉,平時為低電平,一旦發生多卡沖突,此線會升為高電平。在每一次通信過程中,遠端控制器必須通過發送命令來實現任務,典型命令格式為:起始位 S1、

8 位命令字、傳輸數據和結束位ES1。

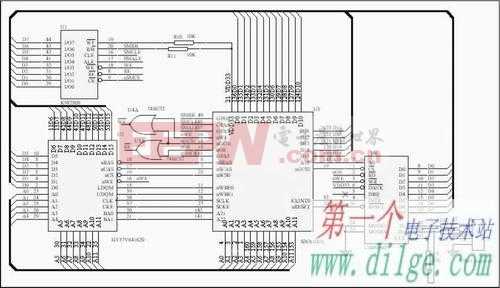

4.嵌入式控制模塊硬件電路設計

S3C44B0X 微處理器是低功耗的,采用了應用于實時環境的 ARM7TDMI 32 位核,所以選為控制模塊的主芯片,負責完成 PC 機和 RFID 讀寫器之間數據的傳送和控制。

4.1 晶振電路

晶振電路用于向 CPU 及其他電路提供工作時鐘。S3C44B0X 芯片通過管腳OM[3:2]確定選擇何種時鐘源,在本系統中,將兩個管腳下拉,選擇晶體時鐘模式,選用該模式時,外部采用 10MHz的晶振,可以利用公式設計出各種所需的輸出頻率,也就是說時鐘頻率可以通過軟件進行設定,公式如下:

Fpllo=( m×Fin ) / ( p×2s)

其中設置 m=0x48,p=0x03,s=0x02,這樣就可以得到 40MHz 的輸出頻率,滿足系統的要求。

4.2 電源電路

在該系統中,需要使用 2.5V 和 3.3V 的直流穩壓電源,其中 S3C44B0X 的內核需 2.5V 電源,S3C44B0X 的 I/O 口和其它部分電路需要 3.3V 電源。為簡化系統電源電路的設計,要求整個系統的輸入電壓為高質量的 5V 的直流穩壓電源,這樣就需要用 DC-DC 轉換器來完成 5V~2.5V 、5V~3.3V 的轉換,在該系統電路中選用了 BayLinear 公司的 B1117 電壓轉換芯片系列:B1117-2.5和B1117-3.3,器件輸出電流為 1.0A。系統電源電路如圖4 所示。

評論