原子頻標中AD9852芯片的應用

在綜合器的研發工作中,實際采用了一微處理器與AD9852配合使用,構成綜合模塊。微處理器完成產生同步鑒相參考脈沖與79Hz鍵控調頻方波信號的功能,通過將微處理器產生的方波信號引入DDS的鍵控調頻引腳,由DDS產生5.3125MHz鍵控調頻信號,經濾波后,送入后續混合電路環節中。

物理機制

在一臺實際的被動型銣原子頻標中,由于各種因素的影響,原子譜線不可能是絕對對稱的,盡管壓控晶振的頻率輸出經射頻倍頻、綜合、微波倍頻混頻后獲得的實際頻率可以精確等于譜線的峰值頻率,但由于實際譜線不對稱,經過伺服環路對量子系統輸出鑒頻信號的處理后,輸出的糾偏電壓中就具有調頻頻率的基波分量,該基波分量是一個偽誤差電壓,會使壓控晶振頻率拉偏,如圖1所示。

圖1 量子系統鑒頻輸出示意圖

若方波調頻的深度保持不變,則這個頻移量也不變,但是由于傳統銣頻標中采用了變容二級管調制電路,變容二級管是溫敏元件,環境溫度變化時,不可避免地將造成方波調頻深度發生變化。顯然,當方波調頻的深度增加時,附加頻移量增加;當方波調頻的深度減小時,附加頻移量減小。因此,銣頻標中的譜線不對稱,將會通過調制電路給銣頻標帶來溫度系數。故在設計時,將調制電路從變容二極管調制方式改為DDS鍵控調頻調制方式。

直接頻率合成

AD9852主要由參考頻率源、相位累加器、波形存儲器(正弦函數功能表)、數模轉換器及低通濾波器組成。參考頻率源為DDS提供工作時鐘頻率,DDS輸出的合成信號的頻率穩定度在不考慮內部諸如附加相位噪聲等環節的影響時,和參考頻率源是一樣的。

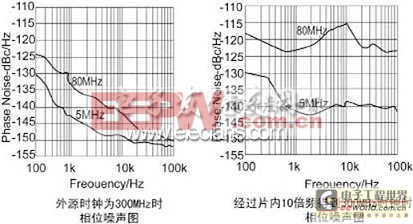

在頻率變換器件中,100Hz和1kHz處的相噪是比較關鍵的技術指標,對用DDS做成的綜合器而言,它取決于DDS輸出信號的相噪、濾波環路的性能以及放大電路的附加相噪等,其后兩項是根據實際設計的濾波及放大電路決定的,對于第一項則取決于實際采用的芯片種類。圖2為一款DDS的輸出相噪圖。

圖2 DDS相噪對比圖

由圖2可見,采用內部倍頻的方式在偏離1kHz、輸出5MHz時相噪為﹣140dBc/Hz;若直接采用300MHz的時鐘時,相噪的性能在偏離1kHz時為﹣142dBc/Hz。因此,為了提高DDS輸出信號的相噪性能,采用外部倍頻法是一個比較好的選擇,即把輸入時鐘信號在外部進行N倍頻后加到DDS上。

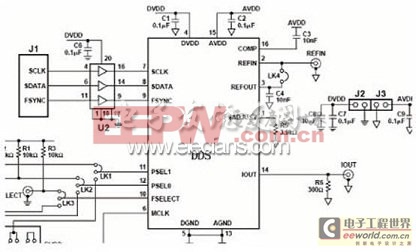

DDS在使用時,要通過微處理器或CPLD對其信號、數據進行管理控制來實現具體應用中所需要的若干功能,圖3為我們選用的一款DDS芯片外圍電路示意圖。

圖3 DDS外圍電路原理圖

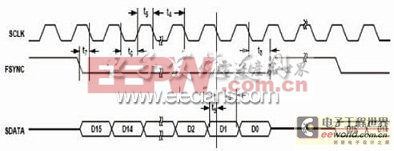

其中,MCLK引腳接外部時鐘源,使DDS的IOUT引腳輸出端頻率信號的穩定度與外部時鐘源一致。對于內部沒有PLL倍頻環節的DDS芯片,通常MCLK端輸入時鐘源的頻率應高于IOUT端輸出信號頻率的4倍。如輸出信號頻率為5.3125MHz,那么MCLK時鐘端的信號頻率應該大于20MHz,以期望得到更好的相位噪聲,通過外部濾波電路后,可得到比較純凈的信號譜。FSELECT為鍵控調頻信號輸入端,也就是我們的調制方波79Hz信號輸入端,我們使用的DDS內部有兩個頻率控制寄存器,通過編程的方式將預先設置好的頻率值F0、F1保存在寄存器中,當FSELECT端有有方波信號輸入時(即電平上升沿或下降沿轉換),DDS的IOUT端將會隨之分別從頻率控制寄存器中讀出F1或F0的值作為輸出,并且會保障頻率信號在切換時相位無變化。PSEL1、PSEL0為兩路信號頻率F1、F0的相位調節端,在應用中,如果需要保持F1、F0在切換時的相位連續,需要在設計中直接將PSEL1、PSEL0接地。DDS與外界通訊的時序是通過引腳FSYNC、SCLK、SDATA來完成的,其串行通訊的時序如圖4所示。

圖4 DDS串行通訊時序示意圖

當FSYNC為高電平時,SCLK、SDATA引腳為高阻狀態。當FSYNC為低電平時,DDS將處于通訊狀態。此時引腳SCLK有一下降沿的脈沖時,將使掛在數據總線SDATA上的DATA寫入DDS數據緩沖區,直至最終一個DATA寫入時,DDS將根據引腳FSELECT上的狀態選擇F1或F0作為IOUT端的輸出。

評論